# Precision Clocking Products Data Book

For Marketing and Application Information Contact:

Applied Micro Circuits Corporation 61.95 Lusk Blvd. San Diego, CA 921.21-2793 (61.9) 450-9333 (800) 755-2622 Fax (619) 450-9885 http://www.arncc.corn The material in this document supersedes all previous documentation issued for any of the products included herein.

AMCC reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

AMCC reserves the right to ship devices of higher grade in place of those of lower grade.

AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Corporate Summary

**5V Clock Drivers**

5V LVTTL I/O Clock Drivers

3.3V Clock Drivers

**Clock Driver Package Specifications**

**5V Clock Generators and Synthesizers**

3.3V Clock Generators

Sales Information

# **C**ONTENTS

| 1. | . PRODUCT SELECTION GUIDES                                |      |

|----|-----------------------------------------------------------|------|

|    | 5V Supply-TTL I/O Clock Driver Products                   | 1-3  |

|    | 5V Supply-LVTTL I/O Clock Driver Products                 |      |

|    | 3.3V Supply-LVTTL I/O Clock Driver Products               | 1-4  |

|    | 5V/3.3V Clock Generator and Synthesizer Products          | 1-4  |

|    | ATM and 100VG AnyLAN Interface Products                   | 1-5  |

|    | Fibre Channel Products                                    | 1-5  |

|    | HIPPI Products                                            | 1-6  |

|    | PCI Bus Products                                          | 1-6  |

|    | SONET/SDH Products                                        | 1-7  |

|    | Crosspoint Switch Products                                | 1-7  |

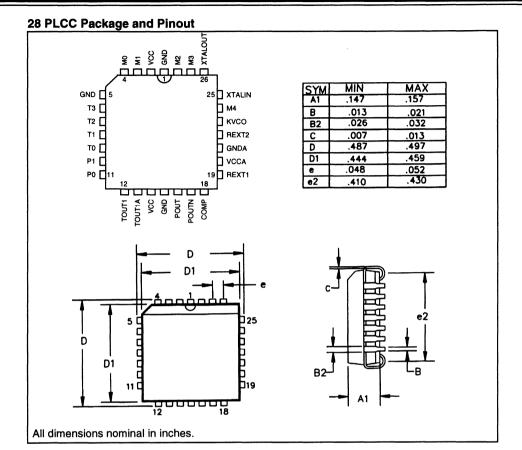

|    | ASIC Products                                             | 1-8  |

| 2. | . CORPORATE SUMMARY                                       |      |

|    | Capability Summary                                        | 2-3  |

|    | Quality System Overview                                   | 2-5  |

| _  |                                                           |      |

| 3. | . 5V CLOCK DRIVERS                                        |      |

|    | A Competitive Edge                                        | 3-3  |

|    | SC3500/06/07/08–20-Output Clock Drivers                   |      |

|    | SC3517/18/28/27/28/29-9 and 10-Output Clock Drivers       | 3-15 |

| 4. | . 5V LVTTL I/O CLOCK DRIVERS                              |      |

|    | SC3306/08–20-Output LVTTL Clock Drivers                   |      |

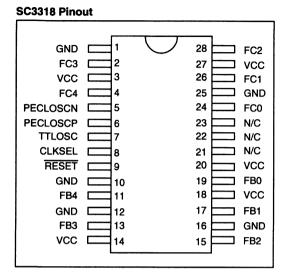

|    | SC3318/27/67/68-10 and 14-Output LVTTL Clock Drivers      | 4-11 |

| 5  | . 3.3V CLOCK DRIVERS                                      |      |

| ٠. | S3LV306/08/18/68–10, 14 and 20-Output LVTTL Clock Drivers | 5-2  |

|    | Clock Driver Application Note                             | 5-13 |

|    | Pentium Application Note                                  | 5-27 |

|    | , G. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1.               |      |

| 6. | . CLOCK DRIVER PACKAGE SPECIFICATIONS                     |      |

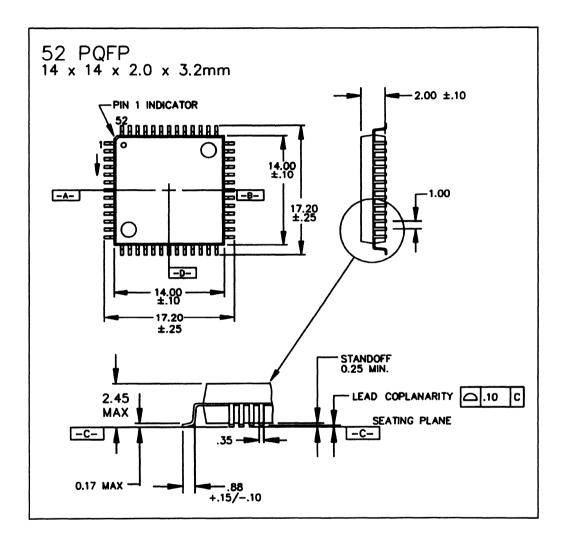

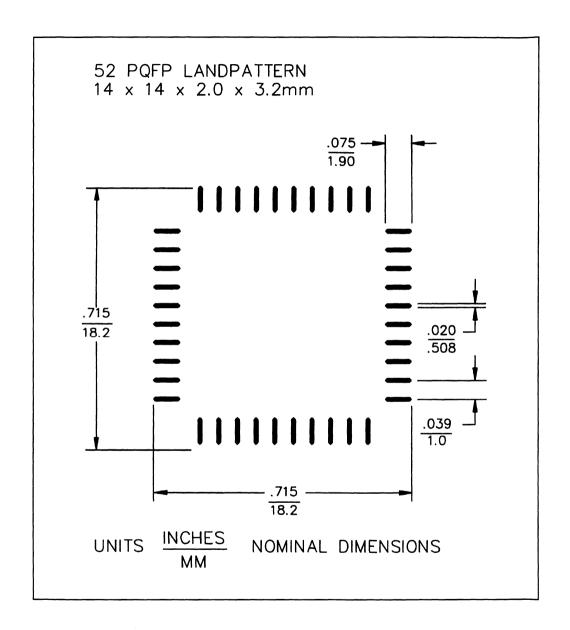

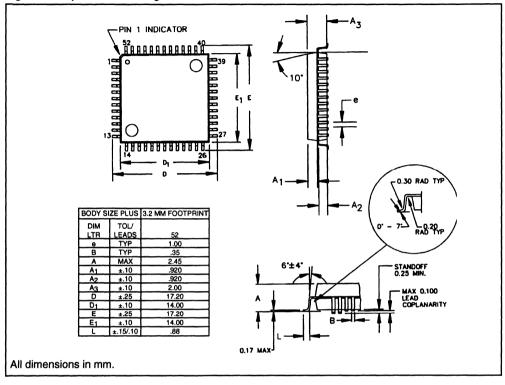

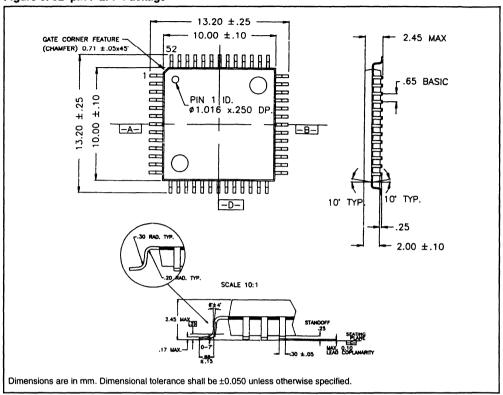

|    | 52-Pin PQFP Mechanical Dimensions                         |      |

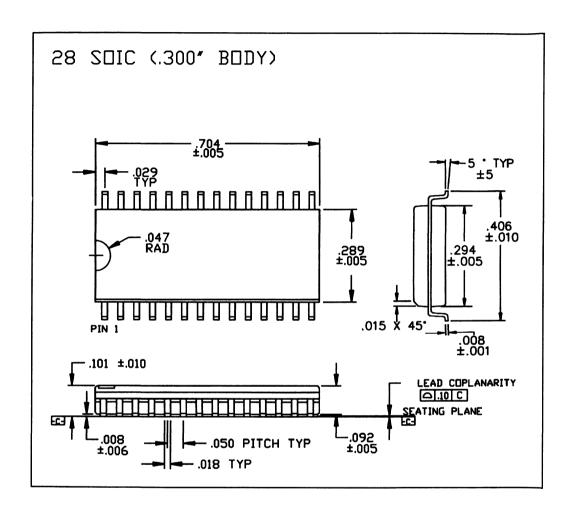

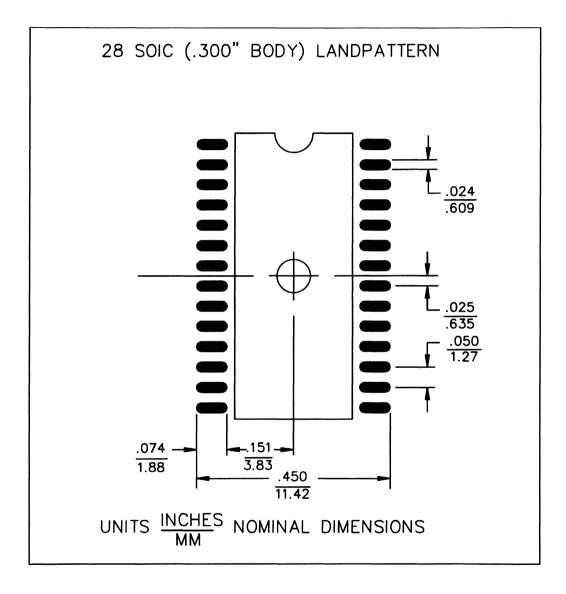

|    | 28-pin SOIC Mechanical Dimensions                         | 6-6  |

| 7. | . 5V CLOCK GENERATORS AND SYNTHESIZERS                    |      |

|    | S4402/S4403-BiCMOS PLL Clock Generators                   | 7-3  |

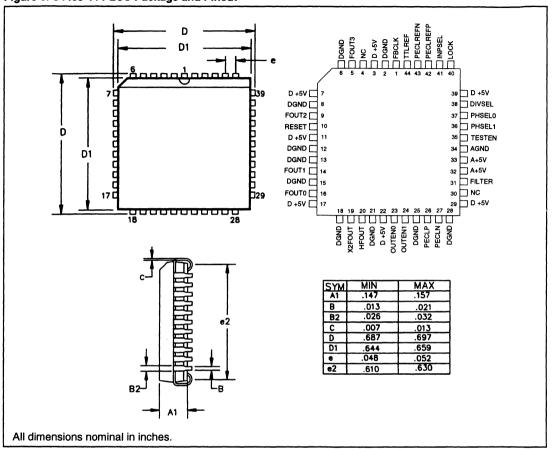

|    | S4405-BICMOS PECL Clock Generator                         |      |

|    | S4406–12-Output BiCMOS PLL Clock Generator                |      |

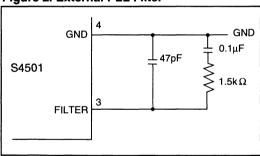

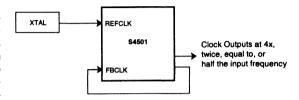

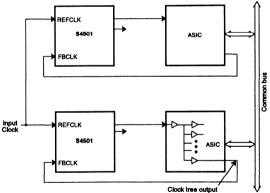

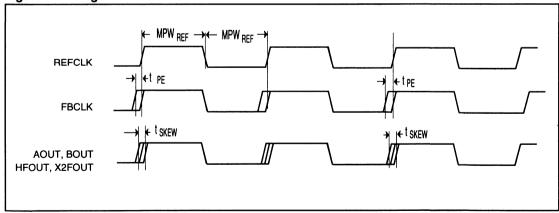

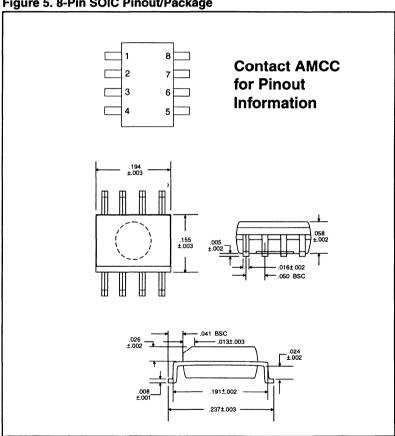

|    | S4501-BiCMOS PLL Clock Multiplier                         |      |

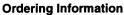

|    | S4503-BICMOS Clock Synthesizer                            | 7-39 |

|    | PLL Clock Generator Application Note                      | 7-49 |

|    | 2 AV OLOOK CENEDATORS                                     |      |

| σ. | . 3.3V CLOCK GENERATORS                                   |      |

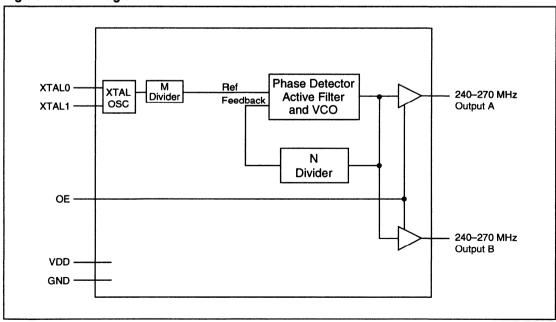

|    | S4LV406–12-Output BiCMOS PLL Clock Generator              | 8-3  |

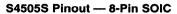

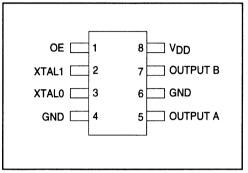

|    | S4505S–RAMBUS™ Compatible Clock Generator                 | 8-9  |

| 9. | SALES INFORMATION                                         |      |

| -  | Sales Information                                         | 0.2  |

|    |                                                           | J-J  |

# **C**ONTENTS

# **PRODUCT SELECTION GUIDES**

| 5V Supply-TTL I/O Clock Driver Products          | 1-3 |

|--------------------------------------------------|-----|

| 5V Supply-LVTTL I/O Clock Driver Products        | 1-3 |

| 3.3V Supply-LVTTL I/O Clock Driver Products      | 1-4 |

| 5V/3.3V Clock Generator and Synthesizer Products | 1-4 |

| ATM and 100VG AnyLAN Interface Products          | 1-5 |

| Fibre Channel Products                           | 1-5 |

| HIPPI Products                                   | 1-6 |

| PCI Bus Products                                 | 1-6 |

| SONET/SDH Products                               | 1-7 |

| Crosspoint Switch Products                       | 1-7 |

| ASIC Products                                    | 1-8 |

# PRODUCT SELECTION GUIDES

# **5V Supply-TTL I/O Clock Driver Products**

|        | W                | Output F<br>ith Respect to  | requency<br>Input Freque    | псу                              |                                        |         |

|--------|------------------|-----------------------------|-----------------------------|----------------------------------|----------------------------------------|---------|

| P/N    | Total<br>Outputs | Number of<br>Outputs<br>+ 1 | Number of<br>Outputs<br>+ 2 | Number of<br>Outputs<br>+ 2 or 4 | Special Features                       | Package |

| SC3500 | 20               | 10                          | 5 + 1 or 2                  | 5                                | _                                      | 52 PQFP |

| SC3506 | 20               | 10                          | 10                          | N/A                              | _                                      | 52 PQFP |

| SC3507 | 20               | 10                          | N/A                         | 10                               | _                                      | 52 PQFP |

| SC3508 | 20               | 20                          | N/A                         | N/A                              | _                                      | 52 PQFP |

| SC3517 | 10               | 5                           | N/A                         | 5                                |                                        | 28 SOIC |

| SC3518 | 10               | 10                          | N/A                         | N/A                              | _                                      | 28 SOIC |

| SC3526 | 9                | 5                           | 4                           | N/A                              | Sync Output                            | 28 SOIC |

| SC3527 | 10               | 3                           | 7                           | N/A                              | Selectable single or dual clock input. | 28 SOIC |

| SC3528 | 10               | 10                          | N/A                         | N/A                              |                                        | 28 SOIC |

| SC3529 | 10               | 10                          | N/A                         | N/A                              | Power Down                             | 28 SOIC |

# **5V Supply-LVTTL I/O Clock Driver Products**

|        |                  | Output Frequence<br>spect to Input Fi | •                                      |                                                        |         |

|--------|------------------|---------------------------------------|----------------------------------------|--------------------------------------------------------|---------|

| P/N    | Total<br>Outputs | Number of<br>Outputs ÷ 1              | Number of<br>Outputs + 2               | Special Features                                       | Package |

| SC3306 | 20               | 10                                    | 10                                     |                                                        | 52 PQFP |

| SC3308 | 20               | 20                                    | N/A                                    |                                                        | 52 PQFP |

| SC3318 | 10               | 10                                    | N/A                                    |                                                        | 28 SOIC |

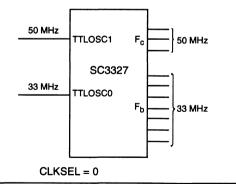

| SC3327 | 10               | 3                                     | 7                                      | Selectable single or dual clock input.                 | 28 SOIC |

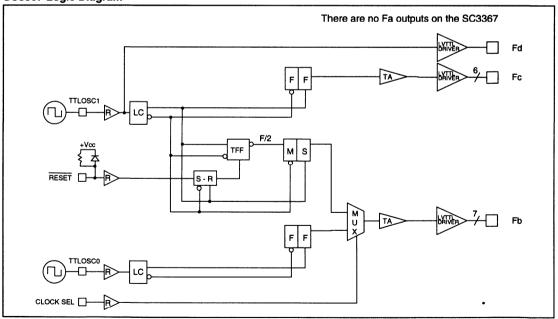

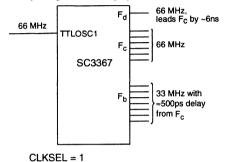

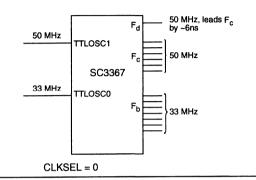

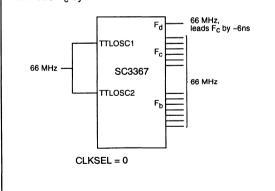

| SC3367 | 14               | 7                                     | 7                                      | Selectable single or dual clock input, 1 output early. | 28 SOIC |

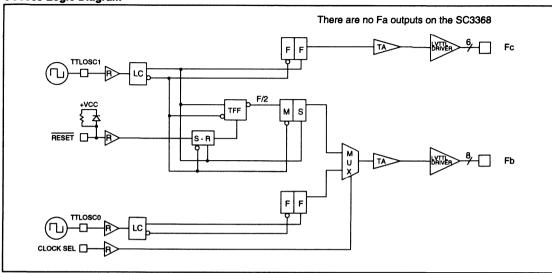

| SC3368 | 368 14 6 8       |                                       | Selectable single or dual clock input. | 28 SOIC                                                |         |

# PRODUCT SELECTION GUIDES

# 3.3V Supply-LVTTL I/O Clock Driver Products

|         | Output Frequency with Respect to Input Frequency |                          |                       |                                        |         |

|---------|--------------------------------------------------|--------------------------|-----------------------|----------------------------------------|---------|

| P/N     | Total<br>Outputs                                 | Number of<br>Outputs + 1 | Number of Outputs ÷ 2 | Special Features                       | Package |

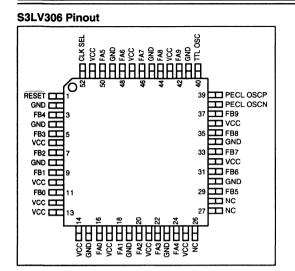

| S3LV306 | S3LV306 20 10                                    |                          | 10                    |                                        | 52 PQFP |

| S3LV308 | 20                                               | 20                       | N/A                   |                                        | 52 PQFP |

| S3LV318 | LV318 10 10                                      |                          | N/A                   |                                        | 28 SOIC |

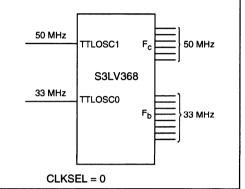

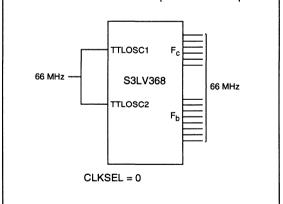

| S3LV368 | 14                                               | 6                        | 8                     | Selectable single or dual clock input. | 28 SOIC |

# 5V/3.3V Clock Generator and Synthesizer Products

|         | w                                                 | Output Fre         |        |                      |               |                                   |                                                    |

|---------|---------------------------------------------------|--------------------|--------|----------------------|---------------|-----------------------------------|----------------------------------------------------|

| P/N     | Description                                       | Input<br>Reference | Number | Туре                 | Max.<br>Freq. | Min. Delay<br>Adjust<br>Increment | Number of<br>Selectable<br>Output<br>Relationships |

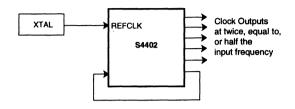

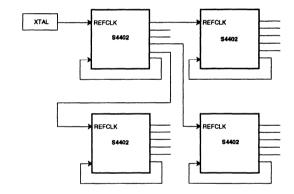

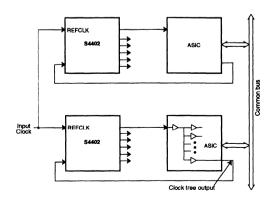

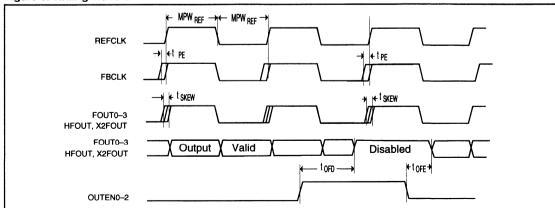

| S4402   | Multiphase Clk<br>Generator                       | TTL                | 6      | ΠL                   | 80            | 3.2 ns                            | 21                                                 |

| S4403   | Multiphase Clk<br>Generator                       | ΠL                 | 10     | ΠL                   | 80            | 3.2 ns                            | 21                                                 |

| S4405   | Multiphase Clk<br>Generator with<br>PECL I/O      | PECL/TTL           | 6<br>1 | TTL<br>PECL          | 80<br>160     | 3.2 ns<br>—                       | 21<br>—                                            |

| S4406   | Clock<br>Generator with<br>Delay Adj. &<br>Invert | ΠL                 | 12     | ΠL                   | 66            | 4 ns @<br>66 MHz                  | 7 x 4 Banks of<br>3 Outputs                        |

| S4501   | Clock Multiplier                                  | ΠL                 | 2      | TTL                  | 100           | N/A                               | 3                                                  |

| S4503   | Clock<br>Synthesizer                              | XTAL               | 2<br>1 | TTL<br>PECL          | 80<br>300     | N/A                               | Multiply 2-32<br>Divide 2-16                       |

| S4505S  | RAMBUS™<br>Compatible<br>Clock<br>Generator       | XTAL               | 2      | RAMBUS<br>Compatible | 270           | N/A                               | 1                                                  |

| S4LV406 | 3.3V Clock<br>Generator                           | ΠL                 | 12     | LVTTL                | 80            | 1.25 ns                           | 7 x 4 Banks of<br>3 Outputs                        |

# **ATM and 100VG AnyLAN Interface Products**

| Product | Function                    | Operating<br>Speed | Data Path   | Package | Power<br>Supply |

|---------|-----------------------------|--------------------|-------------|---------|-----------------|

| S3011   | SONET/ATM/<br>E-4 Tx        | 139/155 Mbit/s     | 8:1 bit     | 80 TEP  | +5.0V           |

| S3012   | SONET/ATM/<br>E-4 Rx        | 139/155 Mbit/s     | 1:8 bit     | 80 TEP  | +5.0V           |

| S3020   | ATM Tx                      | 622 Mbit/s         | 8:1 bit     | 52 TEP  | +5.0V           |

| S3021   | ATM Rx                      | 622 Mbit/s         | 1:8 bit     | 52 TEP  | +5.0V           |

| S2100   | 100VG AnyLAN<br>Transceiver | 120 Mbit/s         | 4:1/1:4 bit | 52 PQFP | +5.0V           |

See Network Interface Products data book.

### **Fibre Channel Products**

| Product | Function                                      | Operating<br>Speed     | Data Path     | Package            | Power<br>Supply |

|---------|-----------------------------------------------|------------------------|---------------|--------------------|-----------------|

| S2036   | Open Fiber<br>Control                         | 266/531/1062<br>Mbit/s | N/A           | 28 SOIC            | +5V             |

| S2042   | Fibre Channel<br>Transmitter                  | 266/531/1062<br>Mbit/s | 10:1/20:1 bit | 44 PQFP<br>52 TQFP | +3.3V           |

| S2043   | Fibre Channel<br>Receiver                     | 266/531/1062<br>Mbit/s | 1:10/1:20 bit | 44 PQFP<br>52 TQFP | +3.3V           |

| S2044   | GLM Compliant<br>Fibre Channel<br>Transmitter | 266/531/1062<br>Mbit/s | 10:1/20:1 bit | 52 TQFP            | +3.3V           |

| S2045   | GLM Compliant<br>Fibre Channel<br>Receiver    | 266/531/1062<br>Mbit/s | 1:10/1:20 bit | 52 TQFP            | +3.3V           |

| S2052   | Fibre Channel<br>Transceiver                  | 266/531/1062<br>Mbit/s | 10:1/1:10 bit | 52 PQFP            | +3.3V           |

| S2060   | 8B/10B<br>Encoder/Decoder                     | 266/531/1062<br>Mbit/s | 10 or 20 bit  | 120 PQFP           | +3.3V           |

See Network Interface Products data book.

# PRODUCT SELECTION GUIDES

# **HIPPI Products**

| Product | Function          | Operating<br>Speed | Data Path | Package             | Power<br>Supply |

|---------|-------------------|--------------------|-----------|---------------------|-----------------|

| S2020   | HIPPI Source      | 800 Mbit/s         | 32 bit    | 225 PGA/<br>208 TEP | -5.2/+5V        |

| S2021   | HIPPI Destination | 800 Mbit/s         | 32 bit    | 225 PGA/<br>208 TEP | -5.2/+5V        |

See Network Interface Products data book.

### **PCI Bus Products**

| Product | Function       | Description       |  |  |

|---------|----------------|-------------------|--|--|

| S5933   | PCI Controller | 32-Bit Add-on Bus |  |  |

See S5933 PCI Controller data book.

### **SONET/SDH Products**

| Product | Function                         | Operating<br>Speed    | Data Path   | Package           | Power<br>Supply |

|---------|----------------------------------|-----------------------|-------------|-------------------|-----------------|

| S3005   | SONET/E-4 Tx                     | 139/155/622<br>Mbit/s | 8:1 bit     | 68 LDCC<br>80 TEP | -4.5/5.0V       |

| S3006   | SONET/E-4 Rx                     | 139/155/622<br>Mbit/s | 1:8 bit     | 68 LDCC<br>80 TEP | -4.5/5.0V       |

| S3014   | CSU/CRU                          | 155/622 Mbit/s        | 1 bit       | 44 PLCC           | -5.2/+5.0V      |

| S3015   | E4/OC-3/STM-1<br>Interface Tx    | 139/155 Mbit/s        | 1 bit       | 52 TEP            | +5V             |

| S3016   | E4/OC-3/STM-1<br>Interface Rx    | 139/155 Mbit/s        | 1 bit       | 52 TEP            | +5V             |

| S3017   | SONET/SDH Tx                     | 622 Mbit/s            | 8:1 bit     | 52 TEP            | +5V             |

| S3018   | SONET/SDH Rx                     | 622 Mbit/s            | 8:1 bit     | 52 TEP            | +5V             |

| S3019   | SONET/SDH<br>/ATM<br>Transceiver | 155/622 Mbit/s        | 1:8/8:1 bit | 52 PQFP           | +3.3V           |

| S3022   | SONET STPC                       | 155/622 Mbit/s        | 1:8/8:1 bit | 120 TEP           | +5V             |

| S3025   | SONET/SDH<br>CRU                 | 155/622 Mbit/s        | 1 bit       | 16 PLCC           | +5V             |

See Network Interface Products data book.

### **Crosspoint Switch Products**

| Product | Function             | Operating<br>Speed | Data Path | Package  | Power<br>Supply |

|---------|----------------------|--------------------|-----------|----------|-----------------|

| S2016   | Crosspoint<br>Switch | 1.5 Gbit/s         | 16 x16    | 120 TEP  | +5V             |

| S2024   | Crosspoint<br>Switch | 600/800 Mbit/s     | 32x32     | 196 LDCC | -5.2/+5V        |

| S2025   | Crosspoint<br>Switch | 1.5 Gbit/s         | 32x32     | 196 LDCC | +5V             |

See Network Interface Products data book.

# **PRODUCT SELECTION GUIDES**

# **ASIC Products**

| Part<br>Number | Technology       | Equivalent<br>Gates<br>(Full Adder Method) | Number<br>of I/O | Structured<br>Array Blocks |

|----------------|------------------|--------------------------------------------|------------------|----------------------------|

| Q20004         | 1 Micron Bipolar | 671                                        | 28               | None                       |

| Q20010         | 1 Micron Bipolar | 1469                                       | 66               | None                       |

| Q20025         | 1 Micron Bipolar | 4032                                       | 100              | None                       |

| Q20045         | 1 Micron Bipolar | 6782                                       | 128              | None                       |

| Q20080         | 1 Micron Bipolar | 11242                                      | 162              | None                       |

| Q20120         | 1 Micron Bipolar | 18777                                      | 198              | None                       |

| Q20P010        | 1 Micron Bipolar | 928                                        | 34               | 1 GHz PLL                  |

| Q20P025        | 1 Micron Bipolar | 3120                                       | 51               | 1 GHz PLL                  |

| Q20M100        | 1 Micron Bipolar | 13475                                      | 195              | RAM                        |

See Network Interface Products data book.

# **C**ONTENTS

| CORP | PORATE SUMMARY          |     |

|------|-------------------------|-----|

|      | Capability Summary      | 2-3 |

|      | Quality System Overview | 2-5 |

CAPABILITY SUMMARY

### **COMPANY OVERVIEW**

AMCC defines, develops, manufactures and markets application specific standard products (ASSPs) and application specific integrated circuits (ASICs) for high speed, high performance network interface applications. Utilizing CMOS, BiCMOS and proprietary MicroPower Bipolar technology, AMCC provides precision clocking devices and interface solutions for PCI, ATM, SONET, and Fibre Channel standards.

Since 1979, AMCC has designed and produced five generations of semicustom bipolar ECL logic arrays and two generations of BiCMOS logic arrays. AMCC ASIC expertise includes its mixed ECL/TTL interface, phase-locked loop (PLL), precision vernier, skew control, high-speed VCO and controlled edge rate output.

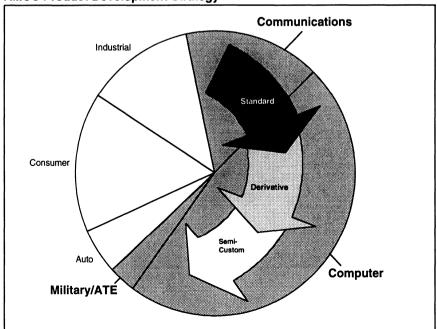

### **AMCC Product Development Strategy**

AMCC's product development strategy utilizes the company's expertise in the computer, communications, ATE and military markets. Initially ASSPs are defined based on key industry standards. Then, as additional applications are identified, derivative products based on the "cores" of the original devices are introduced. The "cores" are then also made available for high volume proprietary ASIC designs.

#### **Network Interface Products**

High performance network interface encompasses a wide range of applications, all requiring data transmission rates from >100 Mbit per second to over 1 Gbit per second, and beyond. These applications include computer data transmission, fiber-optic telecommunications transmission systems, digital video broadcasting and many more.

AMCC interface circuits, transmitter/receiver chip sets and switches are designed to implement emerging network technologies such as the ANSI or ITU approved Asynchronous Transfer Mode (ATM), Synchronous Optical Network (SONET), Fibre Channel, and High Performance Parallel Interface (HIPPI) telecommunications standards. Jitter, speed, power and size are critical design issues of these technologies. AMCC's devices are based on its unique bipolar process which has superior noise isolation characteristics that significantly reduce jitter. The inherent physical structure of the company's process makes 1 to 3 GigaHertz (GHz) data rates possible at relatively low power. The low device power consumption of AMCC's products helps to minimize the cost and size of packaging.

### **CAPABILITY SUMMARY**

# Peripheral Component Interconnect (PCI) Bus Controllers

Increased bandwidth available on high speed networks creates a bottleneck at the desktop. One of the causes of this problem is the latency associated with connection to high speed peripheral equipment, including LANs and WANs. The 132 Megabyte per second backplane PCI bus breaks the bottleneck.

AMCC has developed the industry's first line of general purpose master/slave controllers for the PCI bus. These circuits provide a high performance single-chip interface for add-on boards and adapter cards.

### **Precision Clock and Timing Products**

AMCC provides a growing line of precision clock and timing standard products for exacting system designs. AMCC has also tailored clock and timing devices to specific customer needs for high performance clock generation and distribution, clock synchronization and de-skewing, frequency synthesis, and pulse shaping applications. Offerings include low EMI, low skew clock drivers and low jitter clock generators for high performance server and workstation applications.

### **Strategic Partnerships**

AMCC manufactures its own 1.0 micron BiCMOS and Bipolar wafers using proven processes. The Company follows a "semi-fabbed" manufacturing strategy and has reciprocal foundry relationships in place with major domestic and international semi-conductor partners that provide for significant additional production capacity. Wafer purchases from strategic foundry partners both expand capacity and provide alternate sources. Additional high-volume assembly and test facilities are located offshore.

AMCC's "quick turn, semi-fabbed" manufacturing approach blends together the strengths of both the "fabbed" and "fabless" semiconductor strategies. Fabbed advantages include the security of total inhouse control and time to market. Fabless advantages include multiple sourcing and allows the company to focus investment on new high performance products.

#### AMCC COMMITMENT TO QUALITY

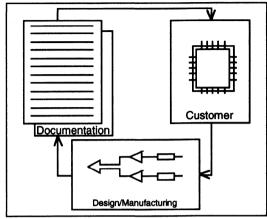

Quality is the degree to which a product meets a customer's expectations with regard to delivery time, cost, and performance to the requirements of the application.

Reliability is "...the probability of a product performing, without failure, a specified function under given conditions for a specified period of time."

AMCC is committed to achieving the highest quality and reliability level in the integrated circuit products we provide. Every year for over a decade we have established industry-leading reliability and outgoing quality targets and then beat them.

The quality and reliability philosophy at AMCC starts with the premise that for AMCC to continue to excel in the ever expanding market place, the quality expectations of customers must be met or exceeded.

Our team operating philosophy is to:

- design in manufacturability and reliability during the new product development phase (plan);

- 2) build in quality at all manufacturing steps (do);

- execute thorough product inspections, internal audits and reliability confirmation (check);

- incorporate feedback from internal and external sources into continuous quality improvement programs (act).

### Reliability and Manufacturability— Designed In From The Start

Reliability and manufacturability is designed in up front through a team infrastructure which focuses on active participation by Design, Manufacturing and Reliability Engineering throughout all phases of the design process. This includes extensive design verification through computer modeling and design validation by product characterization and application simulation. Final team design review and production readiness approval is required prior to release of products to production.

QA gates and subsequent feedback ensures quality confirmation of AMCC's final product in a continuous improvement program.

# Quality Built In During Wafer Fabrication and Manufacturing

AMCC's manufacturing and quality teams employ documented operating procedures, work instructions, in-process inspections and SPC methodology to provide assurance of continued process control and compliance to specification.

### Inspection, Audit and Reliability Confirmation

AMCC has strategically placed In-Process Quality Control (IPQC) gates, internal process/area audits and lot/time specific reliability monitors to verify performance against customer requirements and internal design/manufacturing process capabilities. Metrics generated by these activities are intended to provide continuous improvement feedback data for review and action as driven by senior management.

- · Die visual and precap gate

- · Final outgoing inspection gate

- Modified MIL-STD-105D sampling program

- Lot specific group A and B testing

- · Ongoing reliability monitors

- SPC/Data metric review of key subcontractors

- Visual/mechanical and electrical outgoing indices and PPM goals

- · Cost-of-quality pareto analysis

### **Continuous Quality Improvement Program**

- Corporate-wide commitment driven by the Executive Staff

- A program plan that is flexible enough to comprehend dynamic customer inputs

- Statistical tools in place for analysis and action planning

- Weekly and monthly review meetings to share performance data

- Self examination consistent with elements in ISO9001 and the Malcolm Baldridge National Quality Award

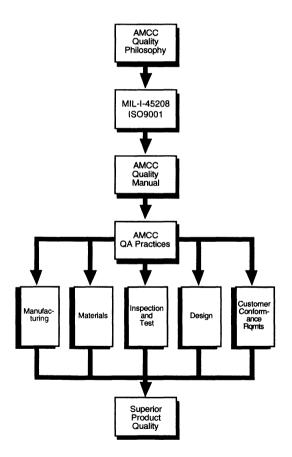

### **AMCC QUALITY SYSTEM**

The Quality System had been modeled after the stringent military requirements of MIL-I-45208, MIL-Q-9858 and MIL-I-38535 Appendix A. Heading into the 21st century, AMCC is now modifying its Quality System to also align with ISO9001. This will strengthen the closed loop improvement cycle by tying internal audits with corrective/preventative action though continuous management review.

AMCC's Quality System has the following components integrated throughout the factory to meet or exceed the above requirements.

- Quality Organization

- · Quality Planning

- Management Review

- Contract Review

- Design Control

- · Document and Data Control

- Purchasing

- · Supplier Selection and Control

- · Control of Customer Supplied Materials

- · Product Identification and Traceability

- · Operating Procedures

- Work Instructions

- · Inspection and Test

- Inspection, Measurement and Test Equipment Calibration

- Inspection Status System

- Control of Nonconforming Material

- Corrective and Preventive Action

- ESD Safe Handling, Storage, Packaging, Preservation and Delivery Methods

- · Records Retention and Maintenance

- Internal Process/Area Auditing System

- · Training/Certification

- SPC and Statistical Techniques

- · Failure Analysis

### **ISO9001 REGISTRATION**

Based on the restructure of the Quality System to ISO9001 requirements and successful completion of internal and third-party audits, AMCC plans to be ISO registered by June of 1996. Please contact the factory for further details and schedule updates.

### PRODUCT QUALIFICATIONS

A qualification is a sequence of tests in which all parameters, including the reliability of the device are tested. It is this sequence of tests which **initially qualifies** the part to be released for production.

Thorough reliability testing is performed on new product and package families in order to ensure the expectations of our customers are met. These tests include environmental, mechanical and life testing performed in accordance with Military Standards, industrial accepted methods and AMCC Test Procedures. Contact the factory for specific details regarding your selected product/package combination.

AMCC provides MIL-STD-883 Methods 5005, 5008, and 5010 testing for our military customers on contract.

### MIL-STD-883 Method 5005

# "Qualification And Quality Conformance Procedures"

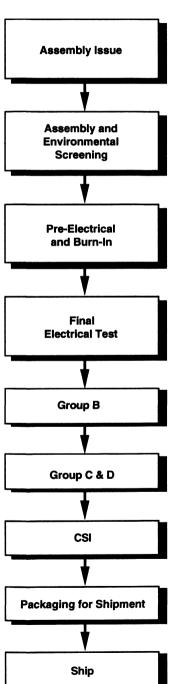

Method 5005 establishes qualification and quality-conformance inspection procedures for semi-conductors to ensure that the quality of devices and lot conform with the requirements of the applicable procurement document. The full requirements of Group A, B, C, D, and E test and inspections are intended for use in initial device qualification—or requalification in the event of product or process change—and in periodic testing for retaining qualification.

**Group A** consists of electrical tests performed on an inspection lot which has already passed the 100% screening requirements. After a lot has passed the 100% screen tests, a random sample of parts is selected from the total population of devices to form the inspection lot. The inspection lot is then subjected to these Group A electrical tests.

**Group B** inspection tests are used to monitor the fabrication and assembly processes performed on each inspection lot.

**Group C** consists of a 1000-hour life test conducted to verify die integrity.

**Group D** verifies the material integrity and the reliability of the package.

**Group E** demonstrates the radiation hardness capability of the device. Performed on a generic basis by device type or as required for an application.

### MIL-STD-883 Method 5010

# "Test Procedures For Custom Monolithic Microcircuits"

This method establishes screening and quality conformance procedures for the testing of custom and semicustom monolithic semiconductors to verify Class B or Class S quality and reliability levels. Testing is performed in conjunction with other documentation such as MIL-I-38535 and an applicable detail specification. It establishes the design, material, performance, control, and documentation requirements needed to achieve prescribed levels of device quality and reliability. AMCC can support qualification using this method.

Until August of 1983, the qualification most commonly used was Method 5005. Since that time, the newer revision of MIL-STD-883 includes Method 5010, which is better suited for semicustom devices (logic arrays included). Either qualification is adequate, but it is desirable to use the 5010 qualification procedure in qualifying custom or semicustom devices.

#### Qualification Method 5005 VS. 5010

The primary difference between the two methods is in the Group D test. Method 5005 uses electrically-good devices, where method 5010 uses electrical rejects and package-only parts for environmental tests. In addition, Method 5010 is designed for smaller production releases (i.e., 2000 devices/year) while Method 5005 is designed for large production releases.

### **Generic Data**

Under the provision of MIL-I-38535, a customer can elect to qualify using generic data (similar device/family). However, the provisions of the applicable contract should be reviewed. In most cases generic data will satisfy full qualification requirements.

Since many of the qualifications at AMCC are ongoing, generic data may be available for this purpose.

- Component Selection

- Definition Specification

- Supplier: Selection Qualification Approval

- Qualified Vendors List (QVL)

- Incoming Inspection

- Acceptance Documents and Operating Procedures

- · Purchase Order

- · Component/Material Specifications

- · Product Assurance and General Procedures

- QVL

- · Sample Inspection of All Direct Materials

- Wafer **Fabrication**

- Class 10 Clean Room FED-STD-209

- Measurements in Adherence with MIL-STD-977

- · SPC:

- In-process Monitors

- PCM Electricals

- SEM Inspection on All Military Lots

- QA Audits

- CV Plots

--- Weekly (minimum)

• DI Water

- --- Weekly

- Particle Counts

- Bacteria Count

- Airborne Particle Count - Weekly

Wafer **Electrical Test** Wafer **Stores**

Plastic

**Flow**

• Die Shear SPC

Wire Bond SPC

· Lead Trim and Co-

Mold/External Visual

planatary Inspection

Precap Visual

### **AMCC Product Assurance Product Flow Detail**

- IPQC Audit

- Manufacturing **Procedures**

### Hermetic **Military Flow**

- Method 50041

- IPQC

- Customer Source Inspection (CSI)

- Assembly Final Inspection

- Methods 5004 & 50051

- Methods 5004 & 50051

- IPQC

- Group A

### Hermetic **Commercial Flow**

- Method 5004 (No Centrifuge

- IPQC

- Assembly Final Inspection

- 25°C -- 100%

- 0°C & 70°C AQL=0.25% Sample

- Method 50051

- IPQC

- Final Inspection

- Method 5005<sup>1</sup>

- · Performed by **Customer Order**

- Per Order

- IPQC

- Outgoing Inspection

- IPQC

- · Final Inspection

- · Coplanatary Check

- IPQC

- · Outgoing Inspection

1Method 5008 or 5010 available

### **AMCC'S RELIABILITY VIGIL**

AMCC's internal reliability vigil consists of three phases:

- New/changed processes and material qualifications

- · In-process Quality monitors

- · Periodic operating life and environmental testing

# New/Changed Wafer Processes and Material Qualifications

In order to initially release a device to production a standard set of MIL-STD-883 tests must be completed successfully. These tests include:

### Wafer Process and Design

- Operating Life Method 1005

- ESD Characterization Method 3015

- Wire Bond Pull Method 2011

- Thermal Shock or Method 1011 or 1010

Temperature Cycling

### **Package and Related Materials**

Selected Subgroups of MIL-STD-883, Method 5005, Group B and D

AMCC adheres to MIL-I-38535 with regards to changes.

If changes to production released devices are determined to be major, the appropriate qualification testing must be successfully completed prior to change approval.

### **In-Process Quality Monitors**

- CV plots

- · Airborne particle count

- · Bacteria, particle count, and resistivity on DI water

- · ESD work stations and procedures

- · In-line testing of process gases

- Temperature and humidity control

- · SPC in wafer fabrication

- · SEM of all military lots

# Periodic Operating Life and Environmental Testing

- Performed on a product from each process family quarterly.

- 1000 hour operating life test (minimum), Method 5005, Group C.

- Temperature cycling per Method 1010, 100 cycles, condition C: -65°C/150°C

- Environmental testing per AMCC standard test procedures. Consult factory for further details.

### **Final Measure and Assurance of Quality**

The cost of defects depends on when the failure occurs. For example, costs rise significantly as undetected defective ICs are integrated into systems. High quality parts cut costs substantially, and the extra quality built into every AMCC device means added value to our customers.

To achieve maximum quality, AMCC employs 100% testing of all devices, followed by stringent QA sampling.

AMCC performs QA sampling measurements at full specification temperature, both DC and AC, to achieve the tightest AQLs in the industry.

### **RADIATION HARDNESS**

High energy radiation can cause structural changes in the silicon and silicon dioxide crystal lattice by displacing atoms from their normal crystal sites. These changes can be responsible for increased junction leakage, degraded transistor current gain (b), and increased parasitic Si/SiO2 interface leakage currents. The damage is generally induced by neutrons, X-rays, and gamma rays. The effects of the damage induced by this radiation can change both AC and DC parameters, affect functional performance, and, in severe cases, destroy the device.

Certain of AMCC's high performance products are inherently radiation resistant. The radiation resistance of AMCC IC's is the result of the small geometries, the structure of the fabrication process itself, and the use of ECL logic within the device. Contact your AMCC representative regarding radiation resistance characteristics associated with a specific product.

# **C**ONTENTS

# **5V CLOCK DRIVERS**

| A Competitive Edge                                  | . 3-3 |

|-----------------------------------------------------|-------|

| SC3500/06/07/08–20-Output Clock Drivers             | . 3-5 |

| SC3517/18/28/27/28/29–9 and 10-Output Clock Drivers | 3-15  |

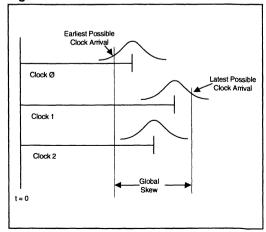

### A COMPETITIVE EDGE

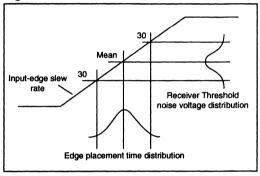

The design of high speed TTL/CMOS systems is often made more challenging and more difficult than their ECL and GaAs counterparts due to the poor transmission line behavior of the TTL device inputs. Since inputs from either TTL or CMOS devices provide essentially no termination to a given signal path (transmission line), reflections at the end of the line are a certainty. Nowhere in a system is this more noticeable and disastrous than when it occurs on the system's clock. It is here that the wrong choice for the clock driver can cripple the chance for success of a design.

There are many contradictions imposed on the "ideal" TTL clock driver. For example, slower edge rates reduce undershoot, ringing and plateau effects at the expense of duty cycle, frequency and clock skew; while faster edge rates cause overshoot, noise injection, and greater EMI radiation while trying to improve frequency, duty cycle and clock skew.

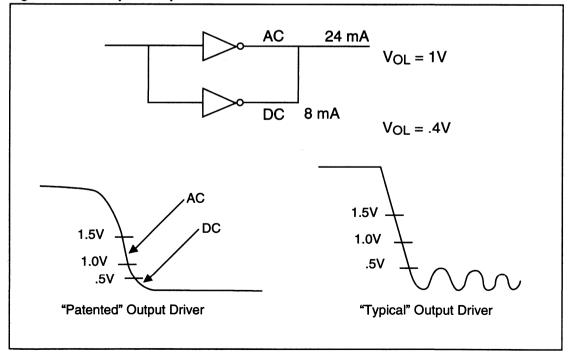

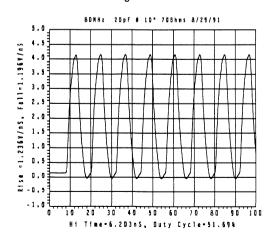

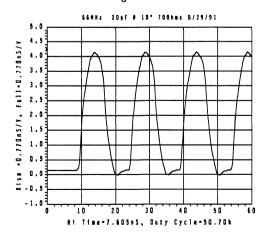

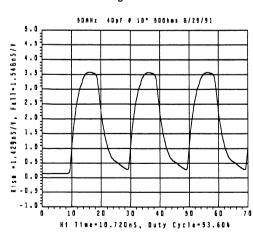

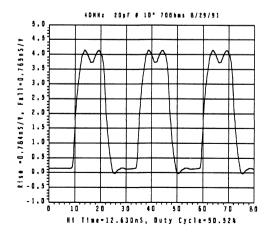

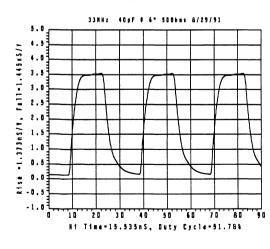

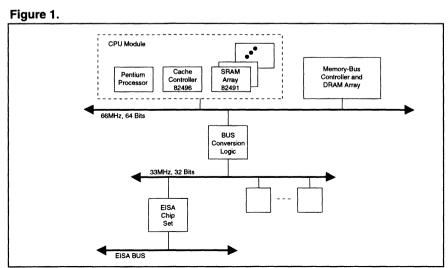

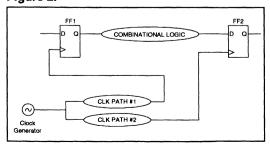

AMCC has solved this dilemma with an output driver circuit that is best described as having two modes for controlling the clock edges. This patented method produces a fast, crisp edge during the transition phase of the output waveform and then immediately slows the edge and becomes a closer match to the impedance of the external PC board. Figure 1 shows the representative effect of the "dual slope" on the falling edge of the clock. The output driver circuit actually uses the reflected wave to determine the appropriate inflection point for the slope and virtually eliminates "ground bounce".

Figure 1. "Dual Sloped" Output Driver Eliminates "Ground Bounce"

### A COMPETITIVE EDGE

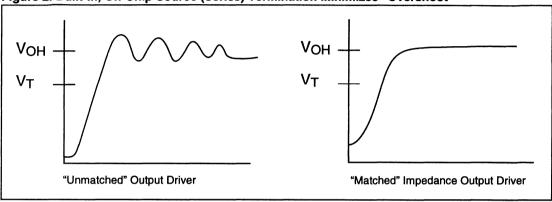

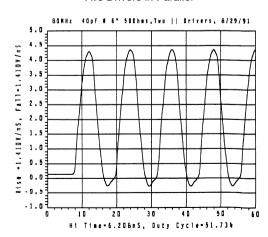

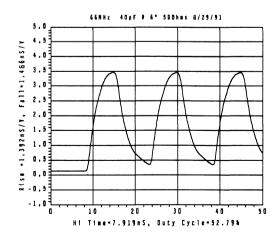

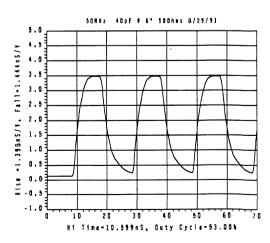

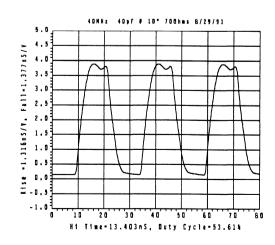

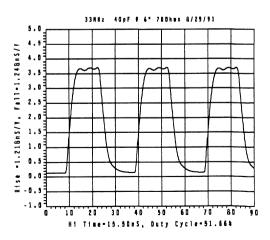

Figure 2 shows the representative effect of dynamically adjusting source series termination on the rising edge. By adjusting the built-in termination to individual loading environments, AMCC's clock drivers prevent "ringing" without the use of any additional onboard termination.

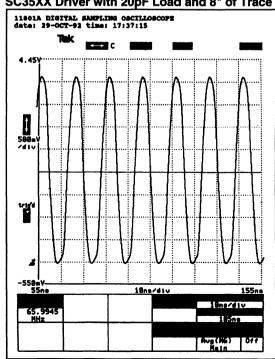

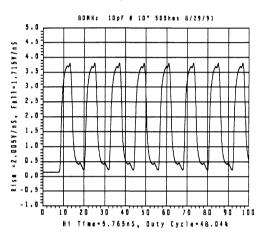

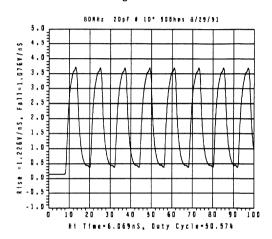

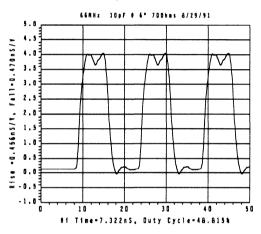

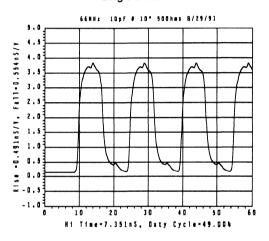

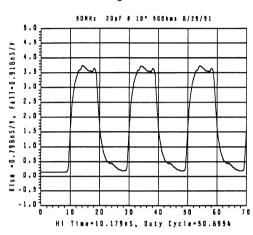

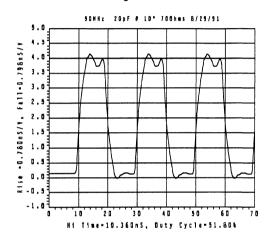

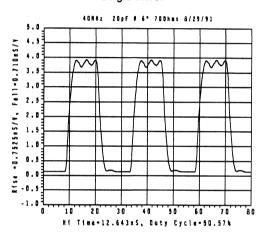

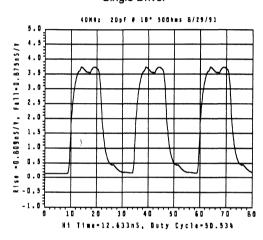

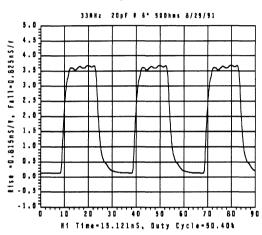

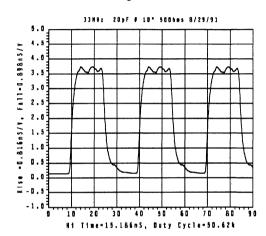

Figure 3 shows an unterminated 66MHz output of an SC35XX Series Driver. Conventional TTL output stages, with or without serial termination resistors, cannot attain both the **edge rates** and the **impedance matching** qualities achieved with the AMCC method.

Figure 2. Built-in, On-Chip Source (Series) Termination Minimizes "Overshoot"

Figure 3. SC35XX Driver with 20pF Load and 8" of Trace

### 20-OUTPUT CLOCK DRIVERS

SC3500/06/07/08

#### **FEATURES**

- 20 clock outputs:

- Grouped into banks of 5 or 10 outputs

- Output frequency of each bank is user selectable

- Leading edge skew for all outputs ≤0.5 ns

- · Proprietary output drivers with:

- Complementary 24 mA peak outputs, source and sink

- 50-75Ω source series termination

- Dynamic drive adjustment to match load conditions

- Edge rates less than 1.5 ns

- Minimizes the ground-bounce, overshoot, and ringing problems often encountered when using CMOS and Bipolar drivers

- 52-pin PQFP package

### **APPLICATIONS**

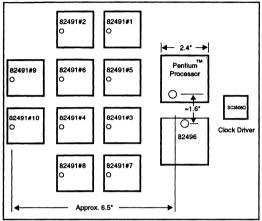

- Compatible with Intel's Pentium<sup>™</sup> processor

- Compatible with PowerPC<sup>™</sup> processors

- PCI Bus clock distribution

- Workstation and server systems with high clock fanout

- Datacom and Telecom networks

### **GENERAL DESCRIPTION**

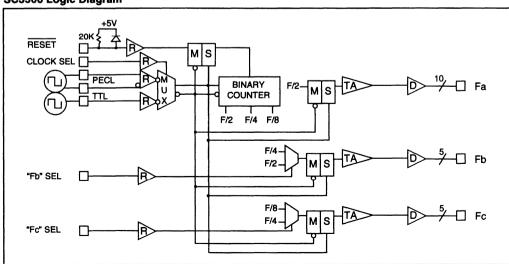

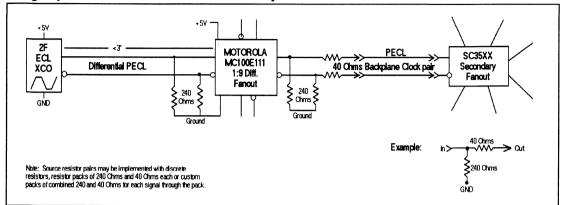

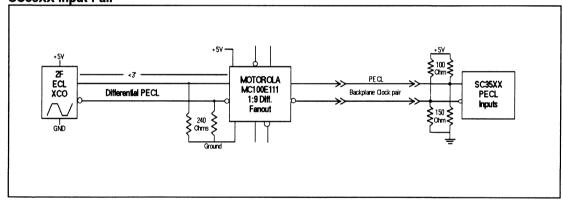

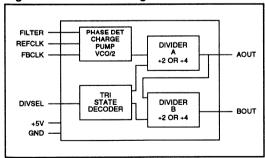

The SC3500, SC3506, SC3507, and SC3508 are precision clock fan out drivers. They accept a reference dock input from either a single-ended TTL source or a differential PECL frequency source. This reference clock input is distributed through dividers and buffers to the output clock drivers.

The 20 outputs are divided into groups of 5 or 10 outputs. The output frequency of each group can be F, F/2, F/4, or F/8, and is user selectable. Each of the clock driver products offers different combinations of divide ratios.

Applied Micro Circuits Corporation (AMCC) uses proprietary complementary (source and sink) 24 mA peak output drivers. In addition to their drive capability, these circuits provide "source (series) termination" at the TTL outputs that minimize over/undershoot without requiring on-board termination networks. They are designed for a maximum output slew rate of ~1.5V/ns to minimize simultaneous output switching noise and distortion.

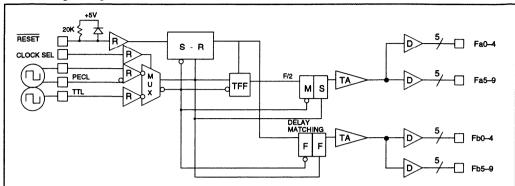

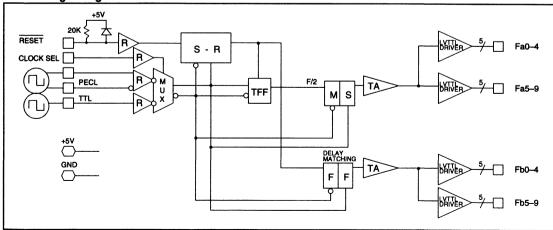

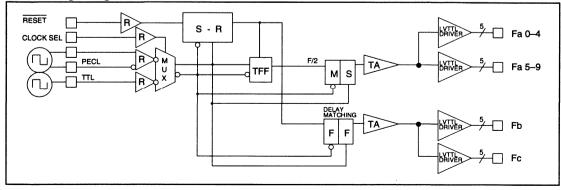

### SC3500 Logic Diagram

### SC3500/06/07/08

### SC3506 Logic Diagram

### SC3507 Logic Diagram

### SC3508 Logic Diagram

# 20-OUTPUT CLOCK DRIVERS

### **Absolute Maximum Ratings**

| Storage Temperature                 | 55° to +150°C |

|-------------------------------------|---------------|

| V <sub>CC</sub> Potential to Ground |               |

| Input Voltage                       |               |

| Static Discharge Voltage            |               |

| Maximum Junction Temperature        |               |

| Latch-up Current                    |               |

| Operating Ambient Temperature       |               |

### Capacitance (package and die total)

| Input Pins      | 5.0 | рF |

|-----------------|-----|----|

| TTL Output Pins | 5.0 | рF |

### **Electrical Characteristics**

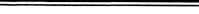

$V_{CC}$  = +5.0V ± 5%,  $T_a$  = 0°C to +70°C (reference "AC Test/Evaluation Circuit")

| Symbol          | Parameter                     | Conditions                                         | Min                  | Max                  | Unit |

|-----------------|-------------------------------|----------------------------------------------------|----------------------|----------------------|------|

| V <sub>IH</sub> | Input HIGH Voltage (PECL)     | Differential Source-PECL                           | V <sub>IL</sub> +0.4 | +V <sub>CC</sub>     | ٧    |

|                 | Input HIGH Voltage (TTL)      | All TTL Inputs                                     | 2.0                  | Vcc                  | V    |

| V <sub>IL</sub> | Input LOW Voltage (PECL)      | Differential Source-PECL                           | V <sub>CC</sub> -2.0 | V <sub>IH</sub> -0.4 | V    |

|                 | Input LOW Voltage (TTL)       | All TTL Inputs                                     | -0.5                 | 0.8                  | ٧    |

| l <sub>IH</sub> | Input HIGH Current (PECL)     | V <sub>IN</sub> = V <sub>CC</sub> (max)            |                      | 200                  | uA   |

|                 | CLKSEL                        | V <sub>IN</sub> = V <sub>CC</sub> (max)            |                      | 350                  | uA   |

|                 | Reset                         | V <sub>IN</sub> = 2.4V                             |                      | -200                 | uA   |

|                 | TTL, CSEL, BSEL               | V <sub>IN</sub> = 2.4V                             |                      | 15                   | uA   |

| IιL             | Input LOW Current (PECL)      | V <sub>IN</sub> = V <sub>CC</sub> -2.0V            |                      | 15                   | uA   |

|                 | CLKSEL                        | $V_{IN} = 0.4V$                                    |                      | 50                   | uA   |

|                 | Reset                         | $V_{IN} = 0.5V$                                    |                      | -325                 | uA   |

|                 | TTL, CSEL, BSEL               | V <sub>IN</sub> = 0.4V                             |                      | 15                   | uA   |

| V <sub>OH</sub> | Output HIGH Voltage           | F <sub>OUT</sub> = 80MHz max C <sub>L</sub> = 10pF | 2.4                  |                      | ٧    |

| V <sub>OL</sub> | Output LOW Voltage            | F <sub>OUT</sub> = 80MHz max C <sub>L</sub> = 10pF |                      | 0.6                  | ٧    |

| lons1           | Output HIGH Short Ckt Current | Output High, V <sub>OUT</sub> = 0V Typ             | -55                  |                      | mA   |

| lous1           | Output LOW Short Ckt Current  | Output Low, V <sub>OUT</sub> = V <sub>CC</sub> Typ | 55                   |                      | mA   |

| PWR             | Static Core Power Dissipation | SC3500, 70°C, Typ Pwr=370 mW                       |                      | 600                  | mW   |

|                 |                               | SC3506, 70°C, Typ Pwr=350 mW                       |                      | 550                  | mW   |

|                 |                               | SC3507, 70°C, Typ Pwr=370 mW                       |                      | 600                  | mW   |

|                 |                               | SC3508, 70°C, Typ Pwr=340 mW                       |                      | 550                  | mW   |

- 1. Maximum test duration, one second.

- The SC3500/06/07/08 features source series termination of approximately 40 Ohms to assist in matching 50–75 Ohm P.C. board environments.

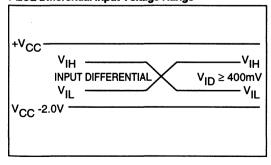

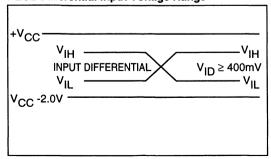

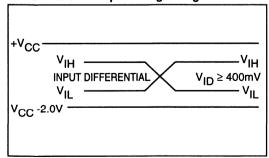

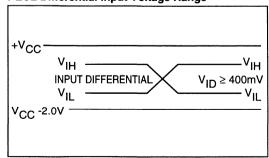

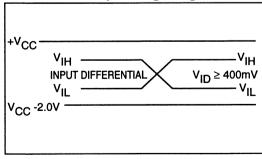

### **PECL Differential Input Voltage Range**

### **DC Characteristics**

The outputs have been designed specifically for clock distribution. In the development of this product, AMCC has made several trade-offs between the historic "high drive, totem pole outputs" and AMCC's dynamically adjusting source series terminated outputs. As a result of this, the outputs will dynamically source and sink a symmetrical 24 mA of current. In a DC state, it exhibits the following specifications:

|                 | Conditions             | Min  | Max  |

|-----------------|------------------------|------|------|

| V <sub>OH</sub> | I <sub>OH</sub> = -8mA | 2.4V |      |

| V <sub>OL</sub> | I <sub>OL</sub> = 4mA  |      | 0.6V |

### AC Specifications—Using "AC Test/Evaluation Circuit"

$V_{CC} = +5.0V \pm 5\%$ , Ta = 0°C to +70°C,  $C_{LOAD} = 10pF$

| Parameter                                 | SC3500     | SC3506            | SC3507     | SC3508            | Units |

|-------------------------------------------|------------|-------------------|------------|-------------------|-------|

| Maximum Skew Across All Outputs           |            |                   |            |                   |       |

| Options: Standard<br>-1<br>-2             | 1.0<br>0.5 | 1.0<br>0.5<br>0.5 | 1.0<br>0.5 | 1.0<br>0.5<br>0.5 | ns    |

| Maximum Skew Chip to Chip                 |            |                   |            |                   |       |

| Options: Standard                         |            | _                 |            | _                 | İ     |

| -1                                        |            | -                 |            | <del></del>       | i     |

| -2                                        |            | 1.0               |            | 1.0               | İ     |

| Maximum Skew within an Output Group       | 0.25       | 0.25              | 0.25       | 0.25              | ns    |

| Maximum Output Duty Cycle Asymmetry       | ±1.0       | ±1.0              | ±1.0       |                   | ns    |

| Maximum TTL Input Frequency               | 80         | 80                | 80         | 80                | MHz   |

| Maximum PECL Differential Input Frequency | 160        | 80                | 160        | 80                | MHz   |

| Maximum Rising/Falling Edge Rate          | 1.5        | 1.5               | 1.5        | 1.5               | ns    |

### Notes:

- 1. Skew is referenced to the rising edges of all outputs.

- Output Duty Cycle Asymmetry is defined as the Duty Cycle deviation from 50%, measured at 1.5V. Duty Cycle will be effected by voltage, temperature, and load (including the length of the PC trace). Only applies to divided outputs.

- Typical skew derating factor for different loads is 50 ps/pF at 1.5V threshold. For example, a 5pF load difference equals a 250 ps skew difference.

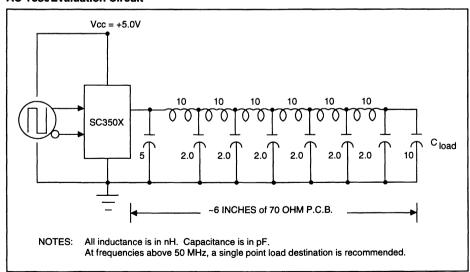

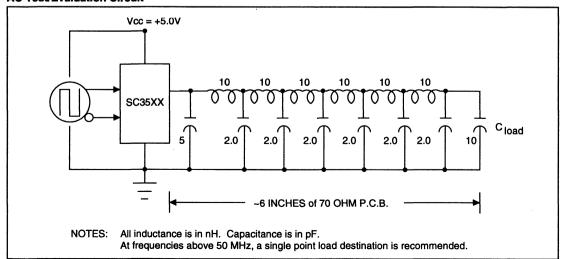

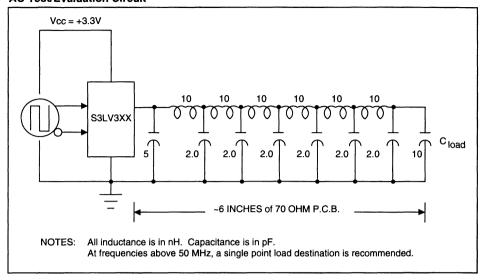

- Edge rates are measured from 0.8V to 2.0V. Load consists of a 6" board trace (70 Ohm) with a 10 pf capacitive load.

See "AC Test/Evaluation Circuit." Synchronous outputs may be paralleled for higher loads.

- 5. Parameters guaranteed by design and characterization.

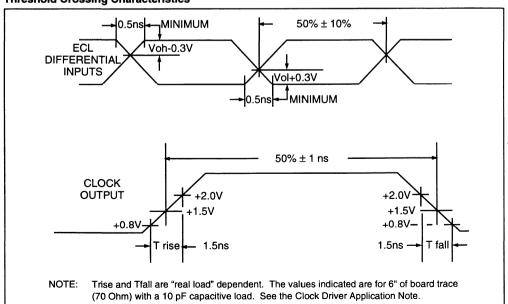

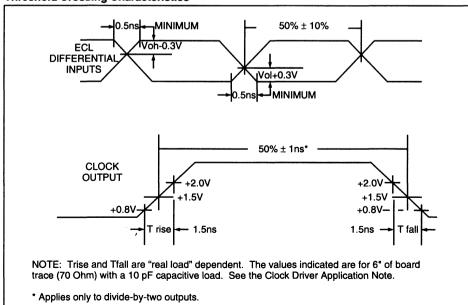

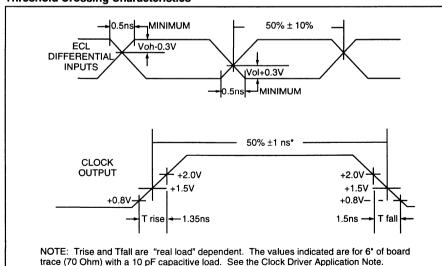

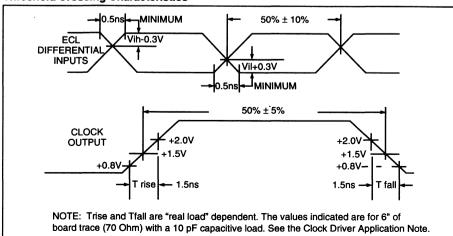

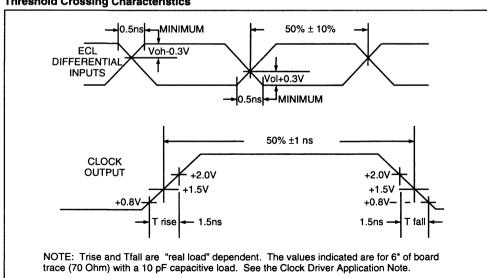

### **Threshold Crossing Characteristics**

# DESCRIPTION OF OPERATION (Refer to Logic Diagrams)

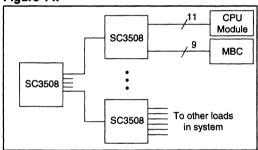

AMCC has developed a single-chip clock shape and 20-output fan-out device using AMCC's advanced BiCMOS process. This design has been optimized for clock symmetry and absolute minimum skew across all twenty outputs.

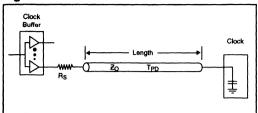

For highest performance this approach requires a clock source input from a crystal-controlled oscillator (XCO) located adjacent to this clock driver. This oscillator, operating between +5V and ground, can provide either differential ECL inputs (referenced to +5V, PECL) or TTL (CMOS) input levels to AMCC's Clock Driver. The input selection is accomplished via the "Clock Sel" input where a "HIGH" level activates the differential ECL input and a "LOW" activates the TTL input. This input clock will be fanned out to a divide-down counter and master-slave flip-flops for synchronization (refer to the Logic Diagrams).

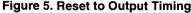

The RESET input is provided to hold off or clear the outputs as may be required by the user's system. This pin may be logically driven from a TTL output. Optionally, if a capacitor  $(4.7\mu F = \sim 100 \text{ ms})$  is connected between this pin and ground, the device will respond with a "power up reset"-a delay in the clock outputs becoming active. At the onset of RESET (low) the outputs will go low following five falling edge clock inputs (four clock inputs for the SC3506 and SC3508). At the expiration of RESET (high) outputs will resume, after five falling edge clock inputs (four clock inputs for the SC3506 and SC3508), from a high (leading edge) count origin (see Figure 5. Reset To Output Timing in the Clock Driver Application Note).

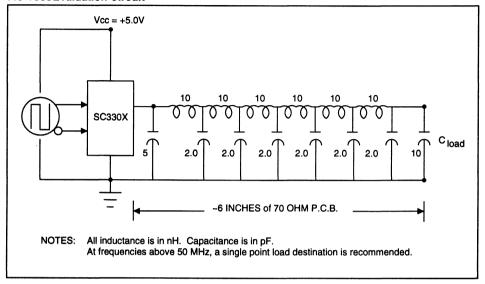

The output drivers are rise and fall slew rate controlled to ~1.5V/ns to minimize noise and distortion resulting from simultaneous switching of the 20 outputs. These outputs also feature series termination (~40 Ohms) to significantly reduce the overshoot and undershoot of non-terminated transmission lines. This will satisfy printed circuit line impedances of 50-75 Ohms terminated into 15 pF (two IC input package receiver pins). When applications require large load capacitance (>25pF with 50 Ohm P.C. board impedance) and/or large peak voltage amplitudes (>3.5 Volts), two adjacent drivers may be paralleled, thereby halving the series resistance and doubling the peak current.

Power and ground are interdigitated with the outputs. Of the 52 package pins, 22 are used for low impedance on-chip power distribution. Due to the simultaneous switching of outputs, low impedance +V<sub>cc</sub> and ground planes within the P.C. board are recommended, as well as substantial decoupling capacitance (see the Clock Driver Application Note for recommendations).

The IC package and die layouts are tightly coupled to assure precise matching of all of the outputs. Collectively, the resistance, inductance, and capacitance of the package and wire bonding is managed to insure that the clock driver will exhibit skews less than the specified maximum. A plastic 52-lead guad flat pack with .039" lead pitch is employed with an outer lead square footprint of approximately 0.7" per side.

#### SC3500/06/07/08 Product Selection Guide

|        | Output Frequency with Respect to Input Frequency |                             |                             |                                  |                  |         |

|--------|--------------------------------------------------|-----------------------------|-----------------------------|----------------------------------|------------------|---------|

| P/N    | Total<br>Outputs                                 | Number of<br>Outputs<br>+ 1 | Number of<br>Outputs<br>+ 2 | Number of<br>Outputs<br>+ 2 or 4 | Special Features | Package |

| SC3500 | 20                                               | 10                          | 5 + 1 or 2                  | 5                                |                  | 52 PQFP |

| SC3506 | 20                                               | 10                          | 10                          | N/A                              | _                | 52 PQFP |

| SC3507 | 20                                               | 10                          | N/A                         | 10                               | _                | 52 PQFP |

| SC3508 | 20                                               | 20                          | N/A                         | N/A                              | _                | 52 PQFP |

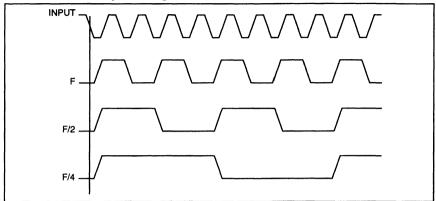

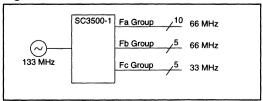

### SC3500 Output Clock Frequency Selection

| "B" SEL | "C" SEL | XCO FREQ | Fa  | Fb  | Fc  |

|---------|---------|----------|-----|-----|-----|

| LO      | LO      | F        | F/2 | F/4 | F/8 |

| н       | LO      | F        | F/2 | F/2 | F/8 |

| LO      | HI      | F        | F/2 | F/4 | F/4 |

| HI      | HI      | F        | F/2 | F/2 | F/4 |

Note: XCO is the input frequency for either the PECL Inputs or the TTL Input. Non-crystal oscillator sources may be used at the user's discretion. See the Clock Driver Application Note.

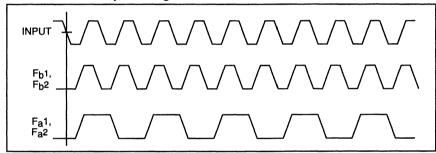

### **SC3507 Output Clock Frequency Selection**

| "B" SEL | "C" SEL | XCO FREQ | Fa1, Fa2 | Fb  | Fc  |

|---------|---------|----------|----------|-----|-----|

| LO      | LO      | F        | F/2      | F/4 | F/4 |

| н       | LO      | F        | F/2      | F/2 | F/4 |

| LO      | н       | F        | F/2      | F/4 | F/2 |

| HI      | ні      | F        | F/2      | F/2 | F/2 |

Note: XCO is the input frequency for either the PECL inputs or the TTL input. Non-crystal oscillator sources may be used at the user's discretion. See the Clock Driver Application Note.

### SC3506 and SC3508 have no frequency selection capabilities.

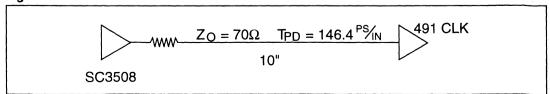

### **AC Test/Evaluation Circuit**

### **Power Management**

The overall goal of managing the power dissipated by the clock driver is to limit its junction (die) temperature to 140°C. A major component of the power dissipated internally by the clock driver is determined by the load that each output drives and the frequency that each output is running. The "Output Power Dissipation" table summarizes these dependencies (see the "AC Test/Evaluation Circuit", for complete load definition).

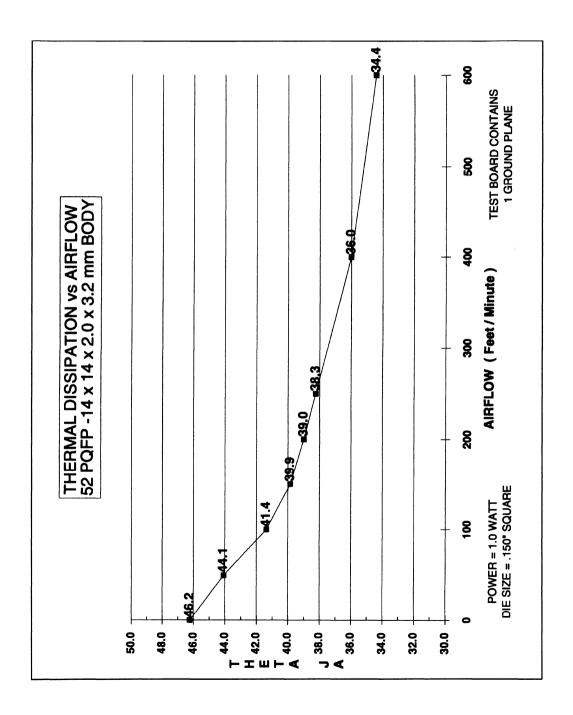

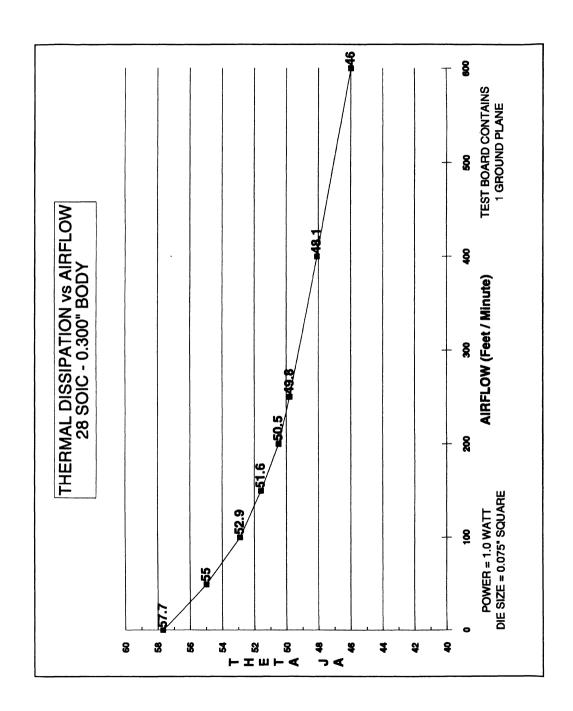

The output power must be added to the core power (600 mW) of the clock driver to determine the total power being dissipated by the clock driver. This total power is then multiplied by the clock driver's thermal resistance, with the result being added to the ambient temperature to determine the junction temperature of the SC350X. For greatest reliability, this junction temperature should not exceed 140°C. The thermal resistance for the clock driver is detailed in the 52-pin PQFP Thermal Dissipation vs. Airflow graph in the Package appendix at the end of this section.

For example: An application utilizes an clock driver with 8 Fa outputs driving 10 pF loads at 66 MHz, 3 Fb outputs driving 5 pF loads at 33 MHz and 2 Fc outputs driving 15 pF loads at 33 MHz. Total chip power is calculated as follows:

| Core Power (SC3500)                                                      | = 600 mW            |

|--------------------------------------------------------------------------|---------------------|

| 8 Fa, 10 pF, 66 MHz = (8 x 47 mW)<br>2 Fa, no load, 66 MHz = (2 x 16 mW) | = 376 mW<br>= 32 mW |

| 3 Fb, 5 pF, 33 MHz = $(3 \times 19 \text{ mW})$                          | = 57 mW             |

| 2 Fb, no load, 33 MHz = (2 x 12 mW)                                      | = 24 mW             |

| 2 Fc, 15 pF, 33 MHz = (2 x 24 mW)                                        | = 48 mW             |

| 3 Fc, no load, 33 MHz = (3 x 12 mW)                                      | = 36 mW             |

Total Power = 1173 mW

The design specifies a 70°C still air ambient. Referring to the 52-pin PQFP Thermal Dissipation vs. Airflow graph in the Package appendix, the  $\Theta_{ja}$  for still air is 46.2°C/watt. The clock driver's junction temperature would then be:

70°C + (1.173 watts x 46.2°C/watt) = 124°C

Note this is below the 140°C maximum junction temperature.

### **Output Power Dissipation**

| FREQUENCY | C <sub>LOAD</sub> =5pF | C <sub>LOAD</sub> =10pF | C <sub>LOAD</sub> =15pF | C <sub>LOAD</sub> =25pF | NO LOAD |

|-----------|------------------------|-------------------------|-------------------------|-------------------------|---------|

| 80 MHz    | 42 mW                  | 51 mW                   | 61 mW                   | 88 mW                   | 18 mW   |

| 66 MHz    | 38 mW                  | 47 mW                   | 55 mW                   | 75 mW                   | 16 mW   |

| 50 MHz    | 28 mW                  | 33 mW                   | 39 mW                   | 60 mW                   | 14 mW   |

| 40 MHz    | 25 mW                  | 30 mW                   | 36 mW                   | 52 mW                   | 13 mW   |

| 33 MHz    | 19 mW                  | 22 mW                   | 24 mW                   | 46 mW                   | 12 mW   |

| 25 MHz    | 16 mW                  | 18 mW                   | 20 mW                   | 32 mW                   | 11 mW   |

| 20 MHz    | 14 mW                  | 16 mW                   | 18 mW                   | 24 mW                   | 10 mW   |

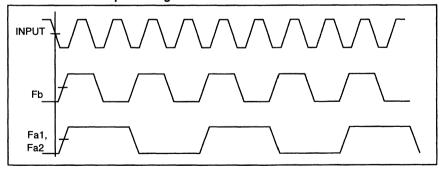

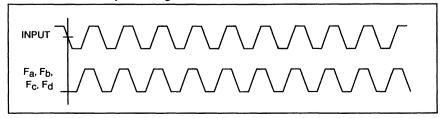

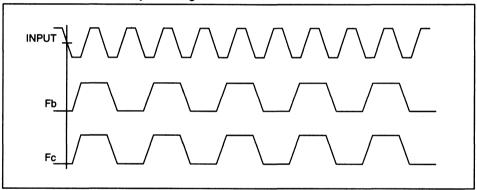

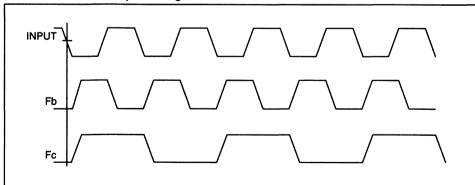

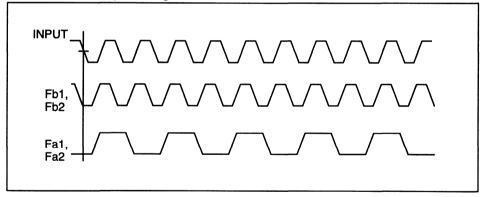

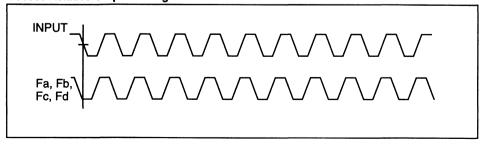

### **SC3500 Relative Output Timing**

# **SC3506 Relative Output Timing**

# **SC3507 Relative Output Timing**

# **SC3508 Relative Output Timing**

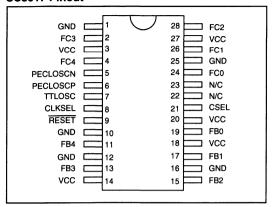

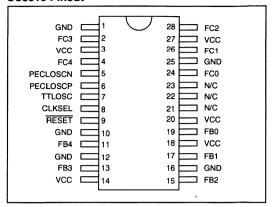

## 20-OUTPUT CLOCK DRIVERS

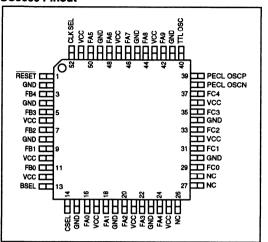

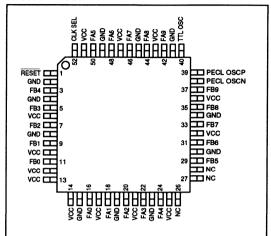

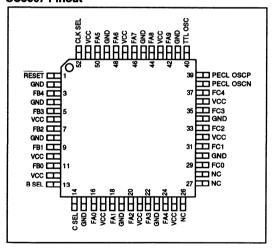

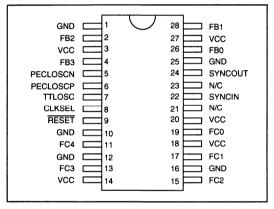

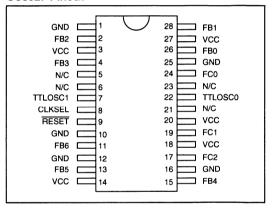

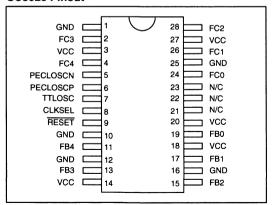

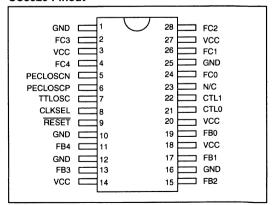

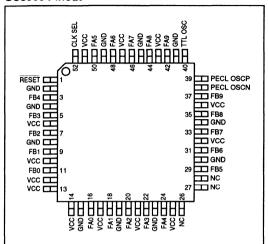

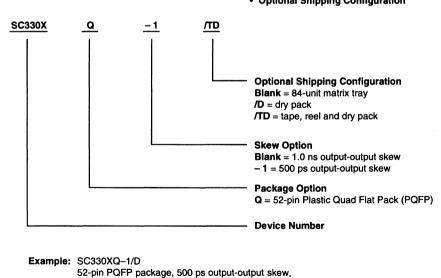

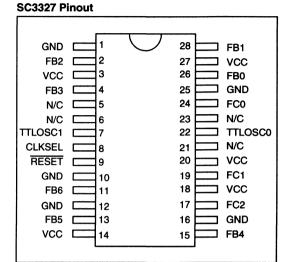

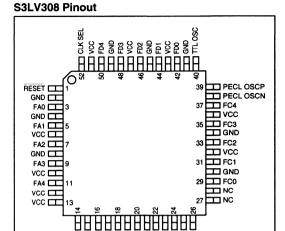

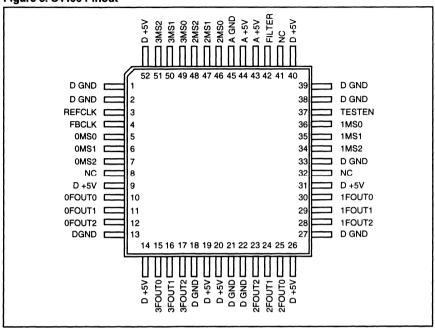

#### SC3500 Pinout

#### SC3506 Pinout

#### SC3507 Pinout

#### SC3508 Pinout

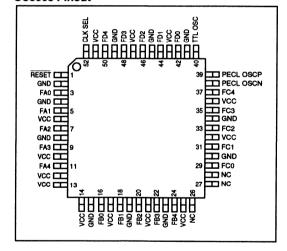

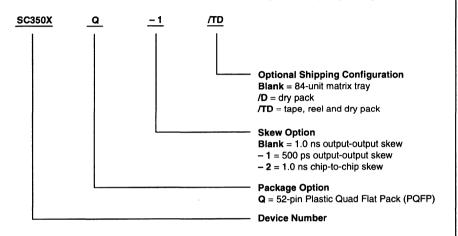

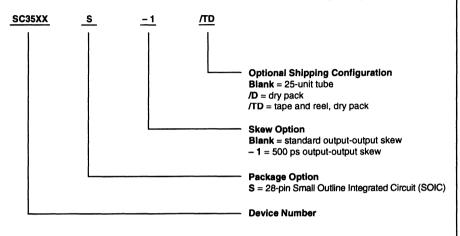

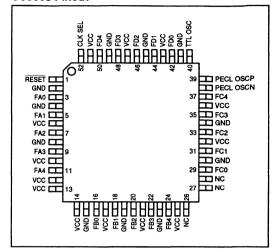

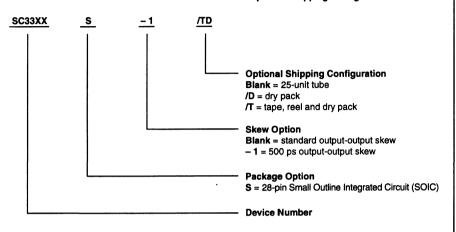

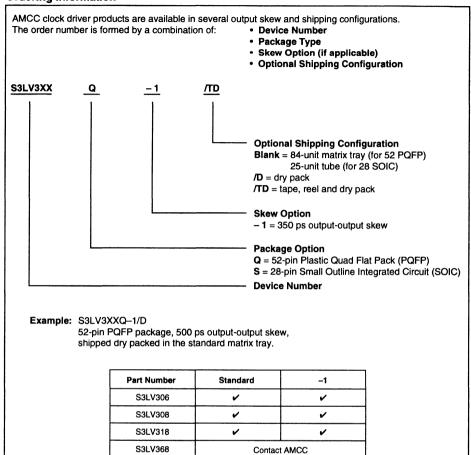

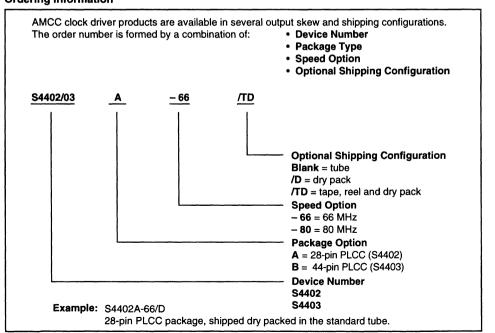

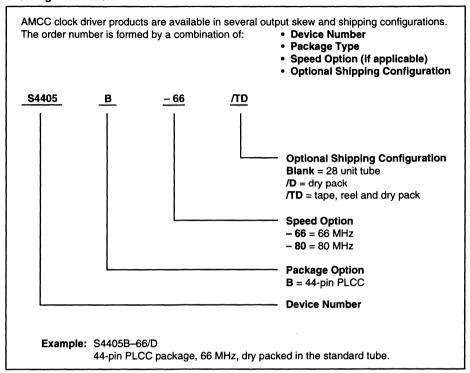

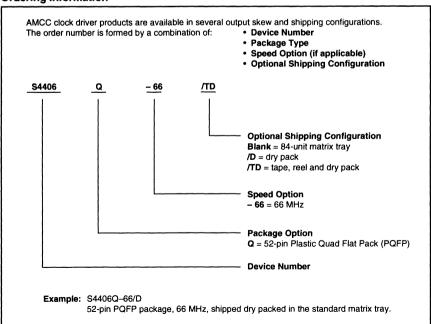

### **Ordering Information**

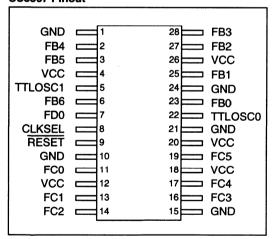

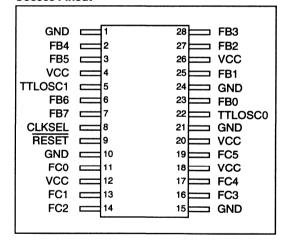

AMCC clock driver products are available in several output skew and shipping configurations.

The order number is formed by a combination of:

- Device Number

- Package TypeSkew Option (if applicable)

- Optional Shipping Configuration

Example: SC350XQ-1/D

52-pin PQFP package, 500 ps output-output skew, shipped dry packed in the standard matrix tray.

| Part Number | Standard | -1 | -2  |

|-------------|----------|----|-----|

| SC3500      | ~        | ~  | N/A |

| SC3506      | ~        | ~  | ~   |

| SC3507      | ~        | ~  | N/A |

| SC3508      | V        | V  | V   |

SC3517/18/26/27/28/29

#### **FEATURES**

- Nine or Ten clock outputs:

- Outputs operate at frequencies, up to 80 MHz

- Outputs grouped in two banks of five outputs on SC3517/18/28/29

- Outputs grouped in a bank of four and a bank of five outputs on the SC3526

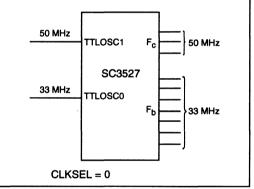

- Outputs grouped in a bank of three and a bank of seven outputs on the SC3527

- Leading edge skew for all outputs ≤0.35 ns

- · Proprietary output drivers with:

- Complementary 24 mA peak outputs, source and sink

- 50-75Ω source series termination

- Dynamic drive adjustment to match load conditions

- Edge rates less than 1.5 ns

- Minimizes the ground-bounce, overshoot, and ringing problems often encountered when using CMOS and Bipolar drivers

- 28-pin SOIC package

#### **APPLICATIONS**

- Compatible with Intel's Pentium™ processor

- Compatible with PowerPC™ processors

- PCI Bus clock distribution

- Workstation and server systems with high clock fanout

- Datacom and Telecom networks

#### GENERAL DESCRIPTION

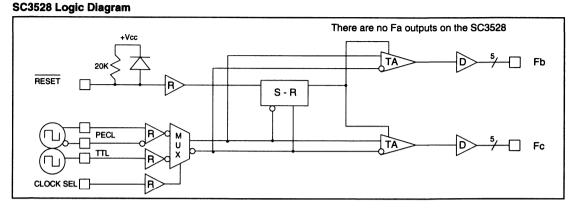

The SC3517, SC3518, SC3526, SC3527, SC3528 and SC3529 are precision low skew clock drivers with nine or ten outputs. They require a clock input from a single-ended TTL or an ECL differential source operating between +5V and ground. This reference frequency input is received and distributed to divide-by-two master-slave flip-flops or to the clock output drivers.

Applied Micro Circuits Corporation (AMCC) uses proprietary complementary (source and sink) 24 mA peak output drivers. In addition to their drive capability, these circuits provide "source (series) termination" at the TTL outputs that minimize over/undershoot without requiring on-board termination networks. They are designed for a maximum output slew rate of ≈1.5V/ns to minimize simultaneous output-switching noise and distortion.

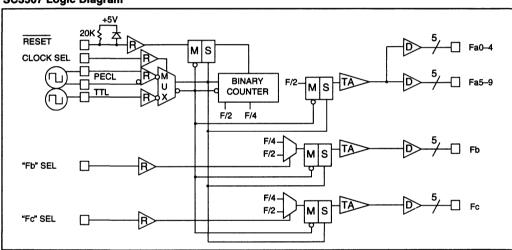

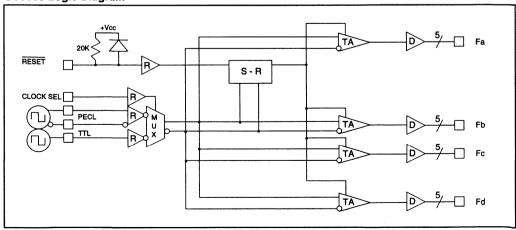

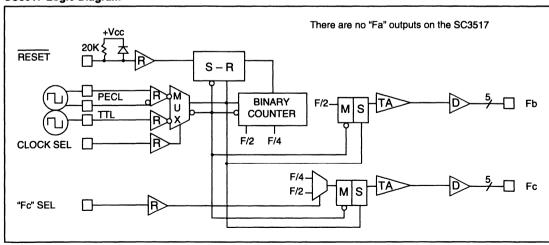

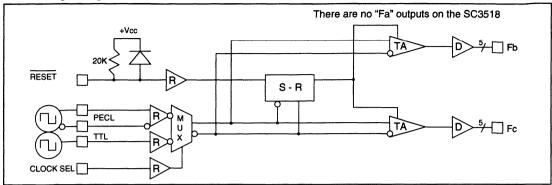

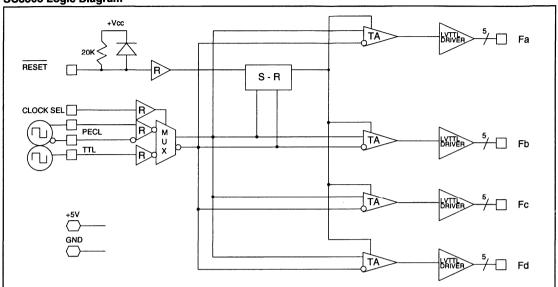

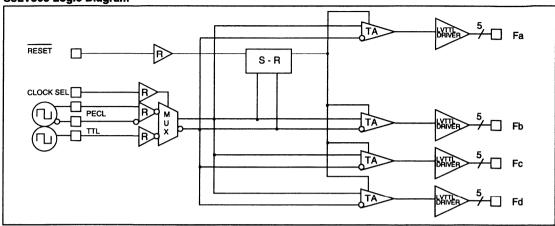

# SC3517 Logic Diagram

# SC3518 Logic Diagram

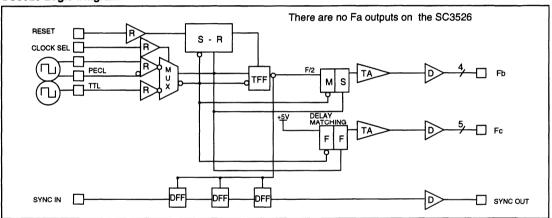

### SC3526 Logic Diagram

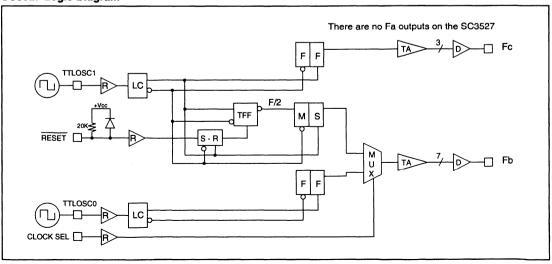

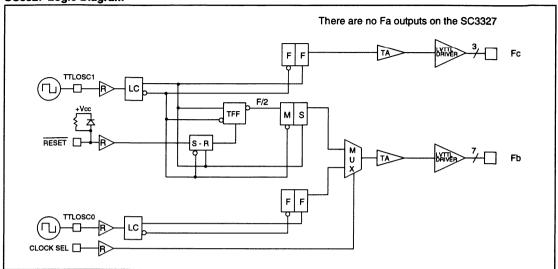

### SC3527 Logic Diagram

#### 222222

9 AND 10-OUTPUT CLOCK DRIVERS

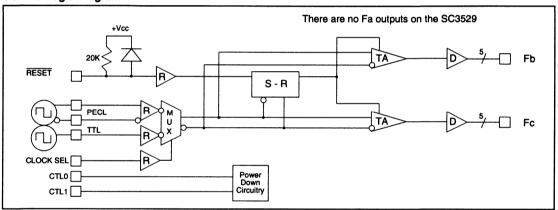

### SC3529 Logic Diagram

#### SC3517/18/26/27/28/29 Product Selection Guide

|        | Output Frequency<br>with Respect to Input Frequency |                             |                             |                                  |                                        |         |

|--------|-----------------------------------------------------|-----------------------------|-----------------------------|----------------------------------|----------------------------------------|---------|

| P/N    | Total<br>Outputs                                    | Number of<br>Outputs<br>+ 1 | Number of<br>Outputs<br>+ 2 | Number of<br>Outputs<br>+ 2 or 4 | Special Features                       | Package |

| SC3517 | 10                                                  | 5                           | N/A                         | 5                                | _                                      | 28 SOIC |

| SC3518 | 10                                                  | 10                          | N/A                         | N/A                              | _                                      | 28 SOIC |

| SC3526 | 9                                                   | 5                           | 4                           | N/A                              | Sync Output                            | 28 SOIC |

| SC3527 | 10                                                  | 3                           | 7                           | N/A                              | Selectable single or dual clock input. | 28 SOIC |

| SC3528 | 10                                                  | 10                          | N/A                         | N/A                              | _                                      | 28 SOIC |

| SC3529 | 10                                                  | 10                          | N/A                         | N/A                              | Power Down                             | 28 SOIC |

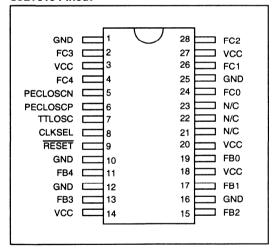

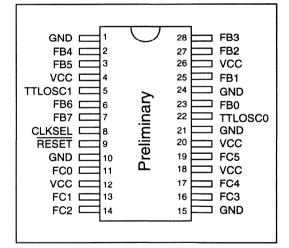

### SC3517/18/26/27/28/29

# 9 AND 10-OUTPUT CLOCK DRIVERS

#### **Absolute Maximum Ratings**

| Storage Temperature                 | 55° to +150°C |

|-------------------------------------|---------------|

| V <sub>CC</sub> Potential to Ground |               |

| Input Voltage                       | 0.5V to +Vcc  |

| Static Discharge Voltage            | >1750V        |

| Maximum Junction Temperature        | +140°C        |

| Latch-up Current                    | >200 mA       |

| Operating Ambient Temperature       | 0° to +70°C   |

### Capacitance (package and die total)

| Input Pins      | .5.0 pF |

|-----------------|---------|

| TTL Output Pins | .5.0 pF |

#### **Electrical Characteristics**

$V_{CC}$  = +5.0V ± 5%,  $T_a$  = 0°C to + 70°C (reference "AC Test/Evaluation Circuit")

| Symbol             | Parameter                     | Conditions                                                    | Min                  | Max                  | Unit     |

|--------------------|-------------------------------|---------------------------------------------------------------|----------------------|----------------------|----------|

| V <sub>IH</sub>    | Input HIGH Voltage (PECL)     | Differential Source-PECL                                      | V <sub>IL</sub> +0.4 | +V <sub>CC</sub>     | ٧        |

|                    | Input HIGH Voltage (TTL)      | All TTL Inputs                                                | 2.0                  | V <sub>CC</sub>      | V        |

| V <sub>IL</sub>    | Input LOW Voltage (PECL)      | Differential Source-PECL                                      | V <sub>CC</sub> -2.0 | V <sub>IH</sub> -0.4 | ٧        |

|                    | Input LOW Voltage (TTL)       | All TTL Inputs                                                | -0.5                 | 0.8                  | V        |

| lін                | Input HIGH Current (PECL)     | V <sub>IN</sub> = V <sub>CC</sub> (max)                       |                      | 200                  | uA       |

|                    | CLKSEL                        | V <sub>IN</sub> = V <sub>CC</sub> (max)                       |                      | 350                  | uA       |

|                    | RESET                         | V <sub>IN</sub> = 2.4V                                        |                      | -200                 | uA       |

|                    | TTL, CSEL                     | V <sub>IN</sub> = 2.4V                                        |                      | 15                   | uA       |

| I <sub>I</sub> L   | Input LOW Current (PECL)      | V <sub>IN</sub> = V <sub>CC</sub> -2.0V                       |                      | 15                   | uA       |

|                    | CLKSEL                        | $V_{IN} = 0.4V$                                               |                      | 25                   | uA       |

|                    | RESET                         | $V_{IN} = 0.5V$                                               |                      | -325                 | uA       |

|                    | TTL, CSEL                     | V <sub>IN</sub> = 0.4V                                        |                      | 15                   | uA       |

| Voh                | Output HIGH Voltage           | F <sub>OUT</sub> = 80MHz max C <sub>L</sub> = 10pF            | 2.4                  |                      | ٧        |

| V <sub>OL</sub>    | Output LOW Voltage            | F <sub>OUT</sub> = 80MHz max C <sub>L</sub> = 10pF            |                      | 0.6                  | V        |

| I <sub>OHS</sub> 1 | Output HIGH Short Ckt Current | Output High, V <sub>OUT</sub> = 0V Typ                        | -55                  |                      | mA       |

| I <sub>OLS</sub> 1 | Output LOW Short Ckt Current  | Output Low, V <sub>OUT</sub> = V <sub>CC</sub> Typ            | 55                   |                      | mA       |

| PWR                | Static Core Power Dissipation | SC3517, 70°C, Typ Pwr=370 mW                                  |                      | 600                  | mW       |

|                    |                               | SC3518, 70°C, Typ Pwr=250 mW                                  |                      | 425                  | mW       |

|                    |                               | SC3526, 70°C, Typ Pwr=225 mW                                  |                      | 375                  | mW       |

|                    |                               | SC3527, 70°C, Typ Pwr=350 mW<br>SC3528, 70°C, Typ Pwr=425 mW  |                      | 350<br>425           | mW<br>mW |

|                    |                               | SC3528, 70 C, Typ PWI=425 IIW<br>SC3529, 70 C, Typ Pwr=250 mW |                      | 425                  | mW       |

<sup>1.</sup> Maximum test duration, one second.

#### **PECL Differential Input Voltage Range**

#### **DC Characteristics**

The outputs have been designed specifically for clock distribution. In the development of this product, AMCC has made several trade-offs between the historic "high-drive, totem-pole outputs" and AMCC's dynamically adjusting source series terminated outputs. As a result of this, the outputs will dynamically source and sink a symmetrical 24 mA of current. In a DC state, it exhibits the following specifications:

|                 | Conditions             | Min  | Max  |

|-----------------|------------------------|------|------|

| V <sub>OH</sub> | I <sub>OH</sub> = -8mA | 2.4V |      |

| V <sub>OL</sub> | I <sub>OL</sub> = 4mA  |      | 0.6V |

The SC3517/18/26/27/28/29 features source series termination of approximately 40 Ohms to assist in matching 50–75 Ohm P.C. board environments.

#### AC Specifications — Using "AC Test/Evaluation Circuit"

$V_{CC} = +5.0V \pm 5\%$ , Ta = 0°C to 70°C,  $C_{LOAD} = 10pF$

| Parameter                                          | SC3517  | SC3518 | SC3526               | SC3527                          | SC3528 | SC3529 | Units          |

|----------------------------------------------------|---------|--------|----------------------|---------------------------------|--------|--------|----------------|

| Maximum Skew Across All Outputs                    |         |        |                      |                                 |        |        |                |

| Options: Standar                                   |         | 0.5    | 0.35<br>—            | _                               | 0.35   | 0.35   | ns             |

| Delay of Fb from Fc outputs<br>(CLKSEL = 1) [Tdly] | _       |        | _                    | Min. 50<br>Typ. 0.9<br>Max. 1.7 | _      | _      | ps<br>ns<br>ns |

| Maximum Skew within an Output Group                | 0.25    | 0.25   | _                    | Fb .50<br>Fc .35                | _      | _      | ns             |

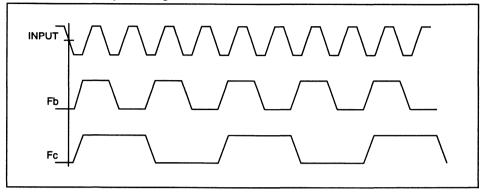

| Maximum Output Duty Cycle Asymmetry                | ±1.0 ns | _      | Min. 45%<br>Max. 55% | Min. 45%<br>Max. 55%            | _      | _      | ns or %        |

| Maximum TTL Input Frequency                        | 80      | 80     | 80                   | 80                              | 80     | 80     | MHz            |

| Maximum PECL Differential Input<br>Frequency       | 160     | 80     | 80                   | 80                              | 80     | 80     | MHz            |

| Maximum Rising/Falling Edge Rate                   | 1.5     | 1.5    | 1.5                  | 1.5                             | 1.5    | 1.5    | ns             |

#### Notes:

- 1. Skew is referenced to the rising edges of all outputs.

- Output Duty Cycle Asymmetry is defined as the Duty Cycle deviation from 50%, measured at 1.5V. Duty Cycle will be affected by voltage, temperature, and load (including the length of the PC trace).

- Typical skew derating factor for different loads is 50 ps/pF at 1.5V threshold. For example, a 5pF load difference equals a 250 ps skew difference.

- Edge rates are measured from 0.8V to 2.0V. Load consists of a 6" board trace (70 Ohm) with a 10 pf capacitive load.

See "AC Test/Evaluation Circuit." Synchronous outputs may be paralleled for higher loads.

- 5. Parameters guaranteed by design and characterization.

#### **Threshold Crossing Characteristics**

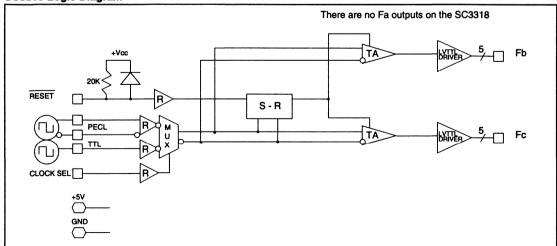

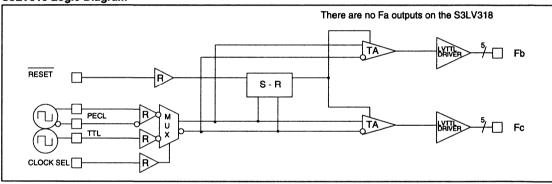

# **DESCRIPTION OF OPERATION** (Refer to Logic Diagram)

AMCC has developed single-chip, nine or ten-output clock buffer drivers using AMCC's advanced BiCMOS process. These designs have been optimized for minimum skew.

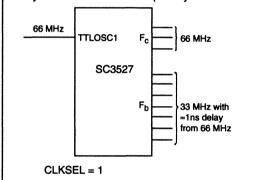

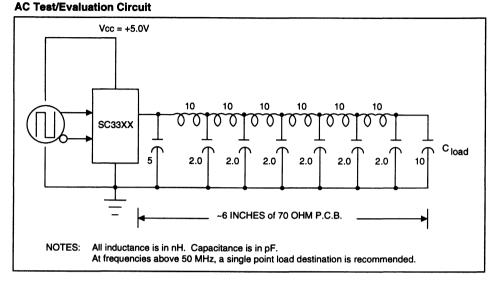

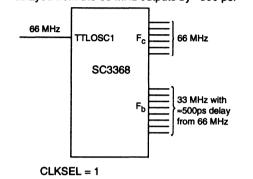

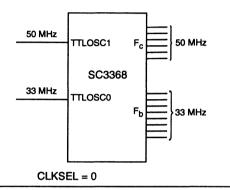

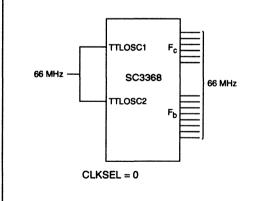

The clock source input for these devices may operate between +5V and ground and can provide either differential ECL inputs (referenced to +5V, PECL) or single-ended TTL (CMOS) levels. This selection is accomplished by use of the CLKSEL pin, where logic LOW (or "float") selects TTL and logic HIGH selects PECL. On the SC3527, when CLKSEL is low (or floating) TTLOSC0 is used to drive the FB0-6 outputs, and when CLKSEL is high, both output groups use the TTLOSC1 reference input clock (see SC3527 Application Examples). This input clock will be fanned out to translation amplifiers and output drivers, refer to the preceding logic diagrams. The output duty cycle asymmetry becomes a function of the output driver slew rate into the AC load for divided outputs. For simple buffered (1x frequency) outputs, the output duty cycle asymmetry becomes a function of the input clock waveshape and the output driver slew rate into the AC load.

The RESET input is provided to hold off or clear the outputs, as may be required by the user's system. This pin may be logically driven from a TTL output. For the products with (pullup) resistors on the RE-SET input, a capacitor (4.7µF ≈ 100 ms) connected between this pin and ground will cause the device to respond with a "power-up reset"—a delay in the clock outputs becoming active. At the assertion of RESET the SC3518/28/29 outputs will go low following four falling edge clock inputs. The SC3527 outputs will go low after three falling edge clock inputs and the SC3517 output will go low after five falling edge clock inputs. At the deassertion of RESET, the SC3518/28/29 outputs will resume operation after four falling edge clock inputs. The SC3527 outputs will resume after three falling edge clock inputs and the SC3517 outputs will resume operation after five falling edge clock inputs.

The RESET input of the SC3526 operates in a different fashion. When RESET is held high (asserted), the FC0-4 outputs will continue to run while the FB0-3 outputs will be driven to a static high. When RESET is de-asserted, the FB0-3 outputs will be active after a fixed three-input clock delay, from a leading edge count origin.

The SC3526 also includes a synchronization circuit. The synchronization circuit provides three serial

flip flops clocked by the internally generated F/2 (half reference frequency) clock which can be used to provide a three-stage metastability filter or a three-cycle delay of the F/2 outputs. The circuit receives its input from the SYNCIN input and feeds the D-input to the first flip-flop; the Q output of the flip-flop feeds the D-input of the second flip-flop which, in turn, feeds the third flip-flop. The Q output of the third flip-flop drives the SYNCOUT pin.

For the SC3529, the CTL0 and CTL1 inputs can be used to "power down" two, five, or ten of the SC3529's outputs. The control circuitry is designed to be synchronous with the reference clock to prevent duty cycle distortion during power-up or power-down sequencing.

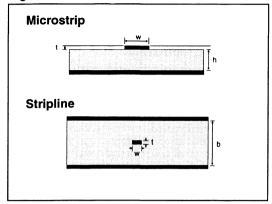

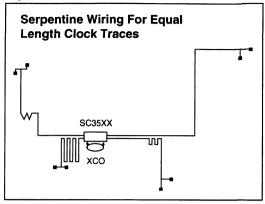

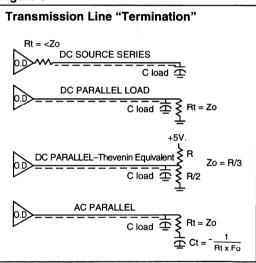

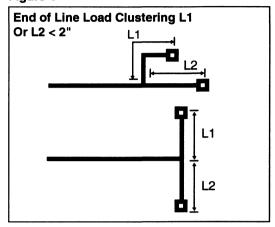

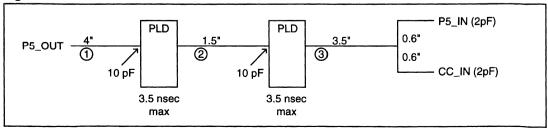

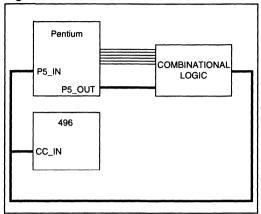

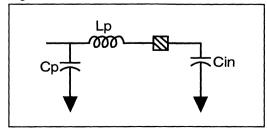

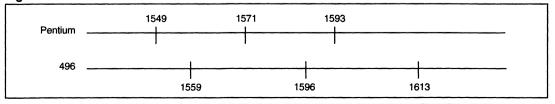

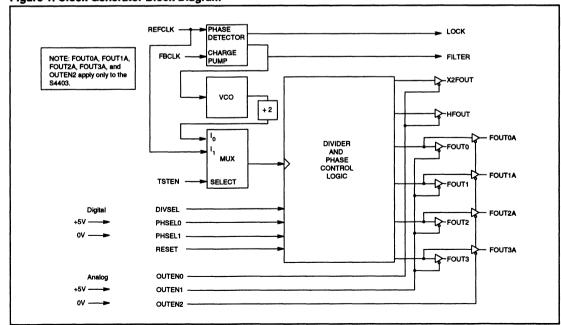

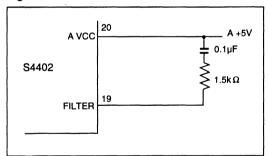

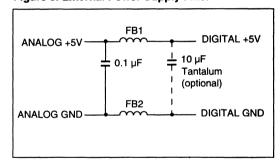

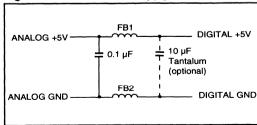

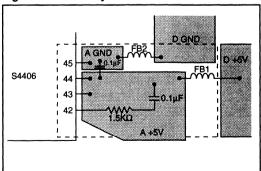

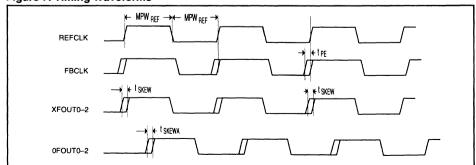

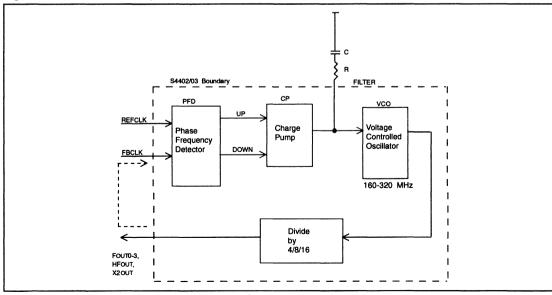

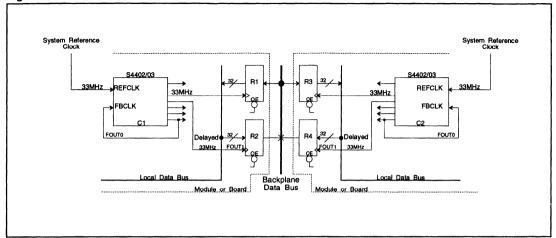

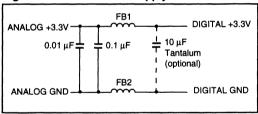

When the inputs are configured (see "SC3529 Input Confliguration table"), the appropriate outputs are driven to the minimum power state (LOW). With all outputs disabled, the power of the device is equal to its static dissipation of 250 mW.